# IS89C51 CMOS SINGLE CHIP 8-BIT MICROCONTROLLER with 4-Kbytes of FLASH

#### **FEATURES**

- 80C51 based architecture

- 4-Kbytes of on-chip Reprogrammable Flash Memory

- 128 x 8 RAM

- Two 16-bit Timer/Counters

- Full duplex serial channel

- Boolean processor

- Four 8-bit I/O ports, 32 I/O lines

- Memory addressing capability

- 64K ROM and 64K RAM

- Program memory lock

- Lock bits (3)

- Power save modes:

- Idle and power-down

- Six interrupt sources

- Most instructions execute in 0.3 μs

- CMOS and TTL compatible

- Maximum speed: 40 MHz @ Vcc = 5V

- Industrial temperature available

- Packages available:

- 40-pin DIP

- 44-pin PLCC

- 44-pin PQFP

#### **GENERAL DESCRIPTION**

The *ISSI* IS89C51 is a high-performance microcontroller fabricated using high-density CMOS technology. The CMOS IS89C51 is functionally compatible with the industry standard 80C51 microcontrollers. The IS89C51 is designed with 4-Kbytes of Flash memory, 128 x 8 RAM; 32 programmable I/O lines; a serial I/O port for either multiprocessor communications, I/O expansion or full duplex UART; two 16-bit timer/counters; an six-source, two-priority-level, nested interrupt structure; and an on-chip oscillator and clock circuit. The IS89C51 can be expanded using standard TTL compatible memory.

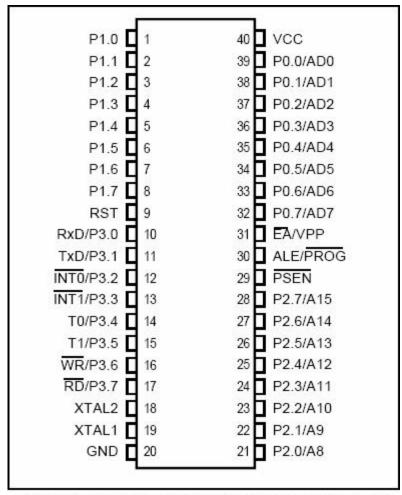

Figure 1. IS89C51 Pin Configuration: 40-pin PDIP

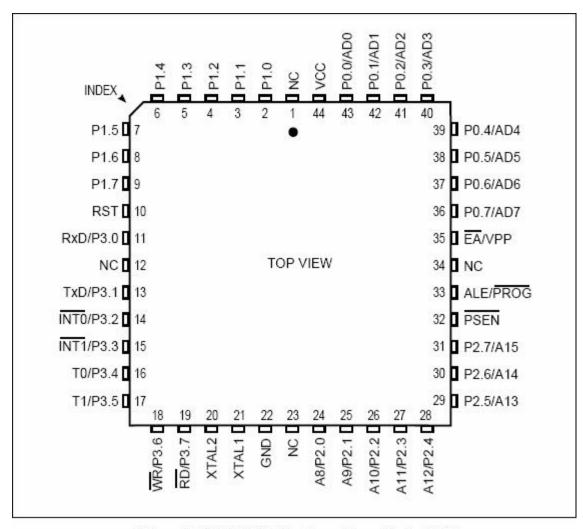

Figure 2. IS89C51 Pin Configuration: 44-pin PLCC

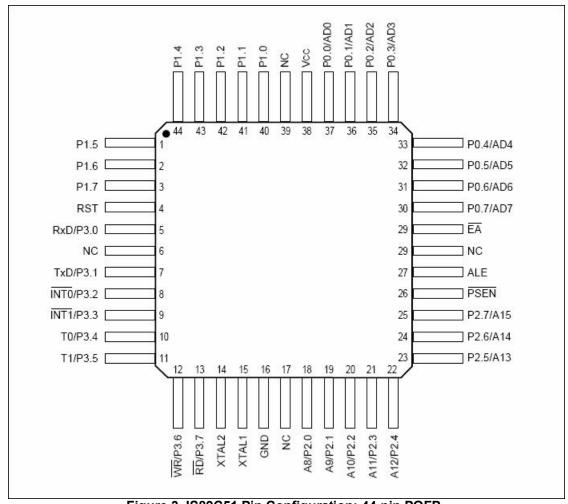

Figure 3. IS89C51 Pin Configuration: 44-pin PQFP

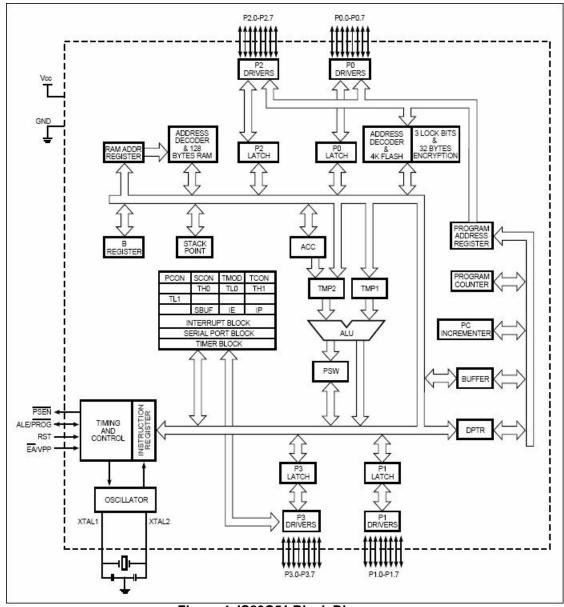

Figure 4. IS89C51 Block Diagram

Table 1. Detailed Pin Description

| of the address during an address to the external memory. We contain personal, AE is emitted at a constant rate of 16 th oscillator frequency, and can be used for external timing of cocking. Note that one ALE public is skepped during ead access to external Cocking. Note that one ALE public is skepped during ead access to external Cocking. Note that one ALE public is skepped during ead access to external Cocking. Note that one ALE public is skepped during ead access to external programming.  EAVIP 31 35 29 I External Access enable: EX must be externally prime memory. This pin is about the Programming and the Vision of Cocking and Cocking. Note that the Alexander Cocking and Cocking a | Symbol                                  | PDIP     | PLCC      | PQFP     | I/O   | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------|-----------|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| enable the device to fetch code from external program memor locations 2009 the TFFFFH. Eas I sheld high, the device executes from internal program memory unless the program counter contains an address greater than 0 FFFH. This also receives the 12V programming enable voltage (Ver) dumin flash programming.  P0.0-P0.7 39-32 43-36 37-30 I/O Port 0: Port 0: Port 0: San 8-bit open-drain, bidrectional I/O port. Port 0: Port  | ALE/PROG                                | 30       | 33        | 27       | I/O   | Address Latch Enable: Output pulse for latching the low byte of the address during an address to the external memory. In normal operation, ALE is emitted at a constant rate of 1/6 the oscillator frequency, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory. This pin is also the Program Pulse input (PROG) during Flash programming.                                                                                                                                                                                                                                                                                                                      |

| P1.0-P1.7   1-8   2-9   40-44   I/O   Port 1: Port 1 is an 8-bit bidirectional I/O port with internal pullup when emitting 1s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | EA/Vpp                                  | 31       | 35        | 29       | ľ     | External Access enable: EA must be externally held low to enable the device to fetch code from external program memory locations 0000H to FFFFH. If EA is held high, the device executes from internal program memory unless the program counter contains an address greater than 0FFFH. This also receives the 12V programming enable voltage (VPP) during Flash programming.                                                                                                                                                                                                                                                                                                                                                               |

| memory programming and outputs the code bytes during program verification. External pullups are required during program verification.  P11.91.7 1-8 2-9 40-44 I/O Port 1: Port 1: s an 8-bit bidirectional I/O port with internal pullups port 1: prise that have 1: written to them are pulled highly by the internal pullups and can be used as inputs. As inputs Port 1: prise that have 1: written to them are pulled highly by the internal pullups and can be used as inputs. As inputs Port 1: prise that have 1: written to them are pulled highly the internal pullups and can be used as inputs. As inputs Port 1: prise that have 1: written to them are pulled highly the port 1: prise that have 1: written to them are pulled highly the internal pullups. See DC Characteristics: highly the internal pullups and can be used as inputs. As inputs Port 2: prise that have 1: written to them are pulled highly the internal pullups and can be used as inputs. As inputs Port 2: prise that have 1: written to them are pulled highly the internal pullups and can be used as inputs. As inputs Port 2: prise that have 1: written 1: prise that have 1: written 1: prise the prise pr | P0.0-P0.7                               | 39-32    | 43-36     | 37-30    | I/O   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| P2.0-P2.7 21-28   24-31   18-25   I/O   Port 2: Port 2 is an 8-bit bidirectional I/O port with internal pullups. And can be used as imputs. As inputs port 1 pins that are externally pulled low will source currer because of the internal pullups. (See DC Characteristics: It., The Port 1 output buffers can sink/source four TTL inputs. Port 1 also receives the low-order address byte during Flast programming and verification.  P2.0-P2.7 21-28   24-31   18-25   I/O   Port 2: Port 2 is an 8-bit bidirectional I/O port with internal pullups. Port 2 pins that have 1s written to them are pulled highly by the internal pullups and can be used as inputs. As inputs Port 2 pins that have 1s written to them are pulled highly by the internal pullups and can be used as inputs. As inputs Port 2 pins that are externally pulled low will source currer because of the internal pullups and can be used as inputs. As inputs and the program and pulled program program memory and during accesses to external data memory that used 16-bit addresses (MOVX @ DPTR). In this application, Port 2 uses strong internal pullups when emittin 1s. During accesses to external data memory that use 4b addresses (MOVX @ DPTR). In this application, Port 2 uses strong internal pullups when emittin 1s. During accesses to external data memory that use 4b addresses (MOVX @ DPTR). In this application, Port 2 uses strong internal pullups and can be used as inputs. As input Port 3 pins that have 1s written to them are pulled highly by the internal pullups. Bort 3 pins that have 1s written to them are pulled highly by the internal pullups. (See DC Characteristics: Iti.) Port 3 also serves the special features of the IS89C51, as liste below.  Port 3 also serves the special features of the IS89C51, as liste below.  RXI 1 19 2 1 15                                                                                                                                                                                                                                                      |                                         |          |           |          |       | memory programming and outputs the code bytes during<br>program verification. External pullups are required during pro-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P2.0-P2.7 21-28 24-31 18-25 I/O Port 2: Port 2 is an 8-bit bidirectional I/O port with intermed pullups. Port 2 pins that have 1s written to them are pulled highly the internal pullups. Port 2 pins that have 1s written to them are pulled highly the internal pullups. Acade as inputs. As inputs. Port 2 pins that have 1s written to them are pulled highly the internal pullups. (See DC Characteristics: III. Port 2 emits the high order address byte during fetches from external program memory and during accesses to external data memory that used 16-bit addresses (MOVX @ DFTR). In this application, Port 2 uses strong internal pullups when emittin 1s. During accesses to external data memory that use 8-bit addresses (MOVX @ Ri [i = 0, 1]). Port 2 emits the contents of the P2 Special Function Register.  Port 2 also receives the high-order bits and some control signals during Flash programming and verification. P2.6 and P2.7 are the control signals while the chip programs and erases.  P3.0-P3.7 10-17 11, 13-19 5, 7-13 I/O Port 3: sone 8-bit bidirectional I/O port with internal pullups. Port 3: pins that have 1s written to them are pulled highly the internal pullups. Gee DC Characteristics: Inc.) Port 3: also serves the special features of the IS89C51, as liste below:  RXD (P3.0): Serial input port.  RXD (P3.1): Serial input port.  RXD (P3.3): Serial input port.  RXD (P3.3): Serial input port.  RXD (P3.3): External interrupt 0.  IXT (P3.3): External interrupt 1.  IXT (P3.3): External data memory write strobe.  PSEN 29 32 26 0 Program Store Enable: The read strobe to external program memory. PSEN acceuting code from the external program memory. PSEN in activated durin fetches from internal program memory. PSEN acceuting code from the external program memory. PSEN acceuting code from the external program memory. P | 200000000000000000000000000000000000000 | 1-8      | 2-9       |          | I/O   | pullups. Port 1 pins that have 1s written to them are pulled high<br>by the internal pullups and can be used as inputs. As inputs,<br>Port 1 pins that are externally pulled low will source current<br>because of the internal pullups. (See DC Characteristics: IL).<br>The Port 1 output buffers can sink/source four TTL inputs.                                                                                                                                                                                                                                                                                                                                                                                                         |

| pullups. Port 2 pins that have 1s written to them are pulled highly the internal pullups and can be used as inputs. As inputs Port 2 pins that are externally pulled low will source currer because of the internal pullups. (See DC Characteristics: liu. Port 2 emits the high order address byte during fetches from external program memory and during accesses to external data memory that use 4:16-bit addresses. (MOVX @ DFTR). In this application, Port 2 uses strong internal pullups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @ RI Pi = 0, 1), Port 2 emits the contents of the P2 Special Function Register.  Port 2 also receives the high-order bits and some control signals while the chip programs and erases.  P3.0-P3.7 10-17 11, 13-19 5, 7-13 I/O Port 3: Port 3 is an 8-bit bidirectional I/O port with internal pullups. Port 3 pins that have 1s written to them are pulled highly byte internal pullups and can be used as inputs. As inputs Port 3 pins that have 1s written to them are pulled highly byte internal pullups. (See DC Characteristics: Liu.)  Port 3 also serves the special features of the IS89C51, as liste below:  10 11 5 1 RxD (P3.0): Serial input port.  11 13 7 0 RxD (P3.1): Serial output port.  11 13 15 9 INTT (P3.3): External interrupt 0.  11 17 (P3.4): External interrupt 1.  12 14 8 INTT (P3.3): External interrupt 1.  13 15 9 INTT (P3.3): External interrupt 1.  14 16 10 I T0 (P3.4): External interrupt 1.  15 17 11 I T1 P3.5; I Timer 1 external input.  16 18 12 0 WR (P3.6): External data memory write strobe.  PSEN 29 32 26 O Program Store Enable: The read strobe to external program memory. When the device is executing code from the external program memory. When the device is executing code from the external program memory. PSEN is activated twice each machine cycle except that two PSEN activations are skipped during each access to external data memory. PSEN is not activated during each case to external program memory. When the device is executing code from the external  |                                         |          |           |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| signals during Flash programming and verification. P2.6 an P2.7 are the control signals while the chip programs an erases.  P3.0-P3.7 10-17 11, 13-19 5, 7-13 I/O Port 3: Port 3 is an 8-bit bidirectional I/O port with internal pullups. Port 3 pins that have 1s written to them are pulled highly by the internal pullups and can be used as inputs. As inputs Port 3 pins that are externally pulled low will source currer because of the internal pullups. (See DC Characteristics: In:) Port 3 also serves the special features of the IS89C51, as liste below:  10 11 5 I RxD (P3.0): Serial input port. 11 13 7 O TxD (P3.1): Serial output port. 12 14 8 I INTO (P3.2): External interrupt 0. 13 15 9 I INTO (P3.3): External interrupt 1. 14 16 10 I T0 (P3.4): Timer 0 external input. 15 17 11 I T1 (P3.5): Timer 1 external data memory write strobe. 17 19 13 O WR (P3.7): External data memory write strobe. 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         | 21-28    | 24-31     | 18-25    | 1/0   | Port 2: Port 2 is an 8-bit bidirectional I/O port with internal pullups. Port 2 pins that have 1s written to them are pulled high by the internal pullups and can be used as inputs. As inputs. Port 2 pins that are externally pulled low will source current because of the internal pullups. (See DC Characteristics: Iu.). Port 2 emits the high order address byte during fetches from external program memory and during accesses to external data memory that used 16-bit addresses (MOVX @ DPTR). In this application, Port 2 uses strong internal pullups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @ Ri [i = 0, 1]), Port 2 emits the contents of the P2 Special Function Register. |

| pullups. Port 3 pins that have 1s written to them are pulled hig by the internal pullups and can be used as inputs. As inputs Port 3 pins that are externally pulled low will source currer because of the internal pullups. (See DC Characteristics: Int) Port 3 also serves the special features of the IS89C51, as liste below:  10 11 5 I RxD (P3.0): Serial input port. 11 13 7 O TxD (P3.1): Serial output port. 12 14 8 I INTO (P3.2): External interrupt 0. 13 15 9 I INTI (P3.3): External interrupt 1. 14 16 10 I T0 (P3.4): Timer 0 external input. 15 17 11 I T1 (P3.5): Timer 1 external input. 16 18 12 O WR (P3.6): External data memory write strobe. 17 19 13 O RD (P3.7): External data memory write strobe. 18 D PSEN 29 32 26 O Program Store Enable: The read strobe to external program memory. When the device is executing code from the external program memory. PSEN is not activated during eac access to external data memory. PSEN is not activated during eac access to external program memory.  RST 9 10 4 I Reset: A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal MOS resisted to GND permits a power-on reset using only an external capacitor connected to Vcc.  XTAL 1 19 21 15 I Crystal 1: Input to the inverting oscillator amplifier and input to the internal clock generator circuits.  XTAL 2 18 20 14 O Crystal 2: Output from the inverting oscillator amplifier.  GND 20 22 16 I Ground: 0V reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |          |           |          |       | Port 2 also receives the high-order bits and some control signals during Flash programming and verification. P2.6 and P2.7 are the control signals while the chip programs and erases.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | P3.0-P3.7                               | 10-17    | 11, 13-19 | 5, 7-13  | I/O   | Port 3: Port 3 is an 8-bit bidirectional I/O port with internal pullups. Port 3 pins that have 1s written to them are pulled high by the internal pullups and can be used as inputs. As inputs. Port 3 pins that are externally pulled low will source current because of the internal pullups. (See DC Characteristics: IIL). Port 3 also serves the special features of the IS89C51, as listed.                                                                                                                                                                                                                                                                                                                                            |

| 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         |          |           |          |       | RxD (P3.0): Serial input port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         | 12       | 14        | 8        | 1     | INTO (P3.2): External interrupt 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         |          |           |          | i     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PSEN 29 32 26 O Program Store Enable: The read strobe to external program memory. When the device is executing code from the external program memory. PSEN is activated twice each machine cycle except that two PSEN activations are skipped during each access to external data memory. PSEN is not activated during fetches from internal program memory.  RST 9 10 4 I Reset: A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal MOS resisted to GND permits a power-on reset using only an external capacitor connected to Vcc.  XTAL 1 19 21 15 I Crystal 1: Input to the inverting oscillator amplifier and input to the internal clock generator circuits.  XTAL 2 18 20 14 O Crystal 2: Output from the inverting oscillator amplifier.  GND 20 22 16 I Ground: 0V reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                         | 16       | 18        | 12       | 0     | WR (P3.6): External data memory write strobe.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RST 9 10 4 I Reset: A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal MOS resists to GND permits a power-on reset using only an external capacitor connected to Vcc.  XTAL 1 19 21 15 I Crystal 1: Input to the inverting oscillator amplifier and input to the internal clock generator circuits.  XTAL 2 18 20 14 O Crystal 2: Output from the inverting oscillator amplifier.  GND 20 22 16 I Ground: 0V reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PSEN                                    | 170 1717 | 1000      | 170 000  | 0.000 | Program Store Enable: The read strobe to external program memory. When the device is executing code from the externa program memory, PSEN is activated twice each machine cycle except that two PSEN activations are skipped during each access to external data memory. PSEN is not activated during                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| XTAL 1 19 21 15 I Crystal 1: Input to the inverting oscillator amplifier and input to the internal clock generator circuits.  XTAL 2 18 20 14 O Crystal 2: Output from the inverting oscillator amplifier.  GND 20 22 16 I Ground: 0V reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RST                                     | 9        | 10        | 4        | E     | Reset: A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal MOS resistor to GND permits a power-on reset using only an externa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| XTAL 2 18 20 14 O Crystal 2: Output from the inverting oscillator amplifier.  GND 20 22 16 I Ground: 0V reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | XTAL 1                                  | 19       | 21        | 15       | I     | Crystal 1: Input to the inverting oscillator amplifier and input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         | 2707     | - 200     | 1782     |       | Crystal 2: Output from the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Vcc 40 44 38 I Power Supply: This is the power supply voltage for operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 800                                     | 20<br>40 | 22<br>44  | 16<br>38 | 1     | Ground: 0V reference.  Power Supply: This is the power supply voltage for operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## **OPERATING DESCRIPTION**

The detail description of the IS89C51 included in this description are:

- Memory Map and Registers

- Timer/Counters

- Serial Interface

- Interrupt System

- Other Information

- Flash Memory

# MEMORY MAP AND REGISTERS Memory

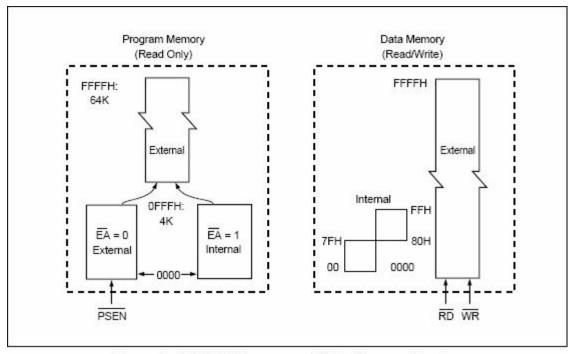

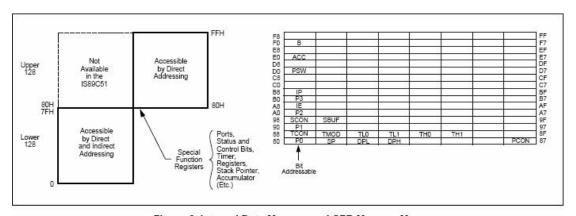

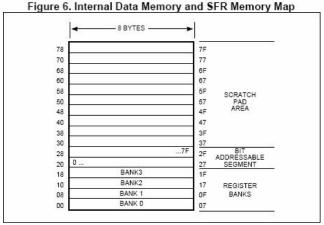

The IS89C51 has separate address spaces for program and data memory. The program and data memory can be up to 64K bytes long. The lower 4K program memory can reside on-chip. Figure 5 shows a map of the IS89C51 program and data memory. The IS89C51 has 128 bytes of on-chip RAM, plus numbers of special function registers. The lower 128 bytes can be accessed either by direct addressing or by indirect addressing. Figure 6 shows internal data memory organization and SFR Memory Map. The lower 128 bytes of RAM can be divided into three segments as listed below and shown in Figure 7.

- 1. **Register Banks 0-3**: locations 00H through 1FH (32 bytes). The device after reset defaults to register bank 0. To use the other register banks, the user must select them in software. Each register bank contains eight 1-byte registers R0-R7. Reset initializes the stack point to location 07H, and is incremented once to start from 08H, which is the first register of the second register bank.

- 2. **Bit Addressable Area:** 16 bytes have been assigned for this segment 20H-2FH. Each one of the 128 bits of this segment can be directly addressed (0-7FH). Each of the 16 bytes in this segment can also be addressed as a byte.

- 3. **Scratch Pad Area:** 30H-7FH are available to the user as data RAM. However, if the data pointer has been initialized to this area, enough bytes should be left aside to prevent SP data destruction.

Figure 5. IS89C51 Program and Data Memory Structure

#### SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFR's) are located in upper 128 Bytes direct addressing area. The SFR Memory Map in Figure 6 shows that. Not all of the addresses are occupied. Unoccupied addresses are not implemented on the chip. Read accesses to these addresses in general return random data, and write accesses have no effect. User software should not write 1s to these unimplemented locations, since they may be used in future microcontrollers to invoke new features. In that case, the reset or inactive values of the new bits will always be 0, and their active values will be 1. The functions of the SFRs are outlined in the following sections, and detailed in Table 2.

#### **Accumulator (ACC)**

ACC is the Accumulator register. The mnemonics for Accumulator-specific instructions, however, refer to the Accumulator simply as A.

#### B Register (B)

The B register is used during multiply and divide operations. For other instructions it can be treated as another scratch pad register.

Program Status Word (PSW). The PSW register contains program status information.

#### Stack Pointer (SP)

The Stack Pointer Register is eight bits wide. It is incremented before data is stored during PUSH and CALL executions. While the stack may reside anywhere in onchip RAM, the Stack Pointer is initialized to 07H after a

reset. This causes the stack to begin at location 08H.

# **Data Pointer (DPTR)**

The Data Pointer consists of a high byte (DPH) and a low byte (DPL). Its function is to hold a 16-bit address. It may be manipulated as a 16-bit register or as two independent 8-bit registers.

#### Ports 0 To 3

P0, P1, P2, and P3 are the SFR latches of Ports 0, 1, 2, and 3, respectively.

#### Serial Data Buffer (SBUF)

The Serial Data Buffer is actually two separate registers, a transmit buffer and a receive buffer register. When data is moved to SBUF, it goes to the transmit buffer, where it is held for serial transmission. (Moving a byte to SBUF initiates the transmission.) When data is moved from SBUF, it comes from the receive buffer.

# **Timer Registers**

Register pairs (TH0, TL0) and (TH1, TL1) are the 16-bit Counter registers for Timer/Counters 0 and 1, respectively.

## **Control Registers**

Special Function Registers IP, IE, TMOD, TCON, SCON, and PCON contain control and status bits for the interrupt system, the Timer/Counters, and the serial port. They are described in later sections of this chapter.

Figure 7. Lower 128 Bytes of Internal RAM