# LAMPIRAN A PERANGKAT LUNAK

#INCLUDE "8051.H"

LED .EQU P3.7

SS .EQU P3.3

KODE .EQU P3.4

## .ORG \$30

DATANOHEX1 .BLOCK 1

DATANOHEX2 .BLOCK 1

DATANOHEX3 .BLOCK 1

DATANOHEX4 .BLOCK 1

DATADECHASIL1 .BLOCK 1

DATADECHASIL2 .BLOCK 1

DATADECHASIL3 .BLOCK 1

DATADECHASIL4 .BLOCK 1

DATADECHASIL5 .BLOCK 1

DATAPENAMBAH1 .BLOCK 1

DATAPENAMBAH2 .BLOCK 1

DATAPENAMBAH3 .BLOCK 1

DATAPENAMBAH4 .BLOCK 1

DATAPENAMBAH5 .BLOCK 1

DATAS1 .BLOCK 1

DATAS2 .BLOCK 1

DATAS3 .BLOCK 1

DATAS4 .BLOCK 1

DATAS5 .BLOCK 1

DATAS6 .BLOCK 1

DATAS7 .BLOCK 1

DATAS8 .BLOCK 1

BUFDATANOMOR .BLOCK 18

STARTDATA .BLOCK 1

DATANOMORASCII1 .BLOCK 1

DATANOMORASCII2.BLOCK 1

```

DATANOMORASCII3.BLOCK 1

```

DATANOMORASCII4.BLOCK 1

DATANOMORASCII5 .BLOCK 1

DATANOMORASCII6.BLOCK 1

DATANOMORASCII7.BLOCK 1

DATANOMORASCII8.BLOCK 1

DATANOMORASCII9.BLOCK 1

DATANOMORASCII10 .BLOCK 1

ENDDATA .BLOCK 1

STKIRIM .BLOCK 1

DATAKIRIM .BLOCK 1

.ORG \$0

LJMP MULAI

.ORG \$23

LJMP SERINT

.ORG \$100

MULAI: MOV SP,#\$20

MOV PSW,#0

MOV R0,#BUFDATANOMOR

SETB LED

MOV STKIRIM,#0

MOV STARTDATA,#\$02

MOV ENDDATA,#\$0D

CLR KODE

LCALL INITSERIAL

SETB ES

SETB EA

## LOOP:

MOV A,STKIRIM

CJNE A,#\$1,KIRIMF

LJMP LOOP

## KIRIMF:

MOV A,#\$FF

MOV DATAKIRIM,A

LCALL KIRIMKEPC

LJMP LOOP

SERINT: JBC RI,GETDATASERIAL

**RETI**

## **GETDATASERIAL**:

PUSH ACC

MOV A,SBUF

CLR RI

CJNE A,#\$03,ISIKEBUFFER

LCALL PROSES

MOV R0,#BUFDATANOMOR

POP ACC

**RETI**

## ISIKEBUFFER:

MOV @RO,A

INC R0

POP ACC

**RETI**

## PROSES:

MOV R0,#BUFDATANOMOR

INC R0

INC R0

INC R0

MOV A,@R0

LCALL CEKA\_F

ANL A,#\$0F

MOV DATAS1,A

INC R0

MOV A,@R0

LCALL CEKA\_F

ANL A,#\$0F

MOV DATAS2,A

INC R0

MOV A,@R0

LCALL CEKA\_F

ANL A,#\$0F

MOV DATAS3,A

INC R0

MOV A,@R0

LCALL CEKA\_F

ANL A,#\$0F

MOV DATAS4,A

INC R0

MOV A,@R0

LCALL CEKA\_F

ANL A,#\$0F

MOV DATAS5,A

INC R0

MOV A,@R0

LCALL CEKA\_F

ANL A,#\$0F

MOV DATAS6,A

INC R0

MOV A,@R0

LCALL CEKA\_F

ANL A,#\$0F

MOV DATAS7,A

INC R0

MOV A,@R0

LCALL CEKA\_F

ANL A,#\$0F

MOV DATAS8,A

## ;-----PENGGABUNGAN

MOV A,DATAS1

SWAP A

ANL A,#\$F0

MOV DATANOHEX1,A

MOV A,DATAS2

ANL A,#\$0F

ORL A,DATANOHEX1

MOV DATANOHEX1,A

MOV A,DATAS3

SWAP A

ANL A,#\$F0

MOV DATANOHEX2,A

MOV A,DATAS4

ANL A,#\$0F

ORL A,DATANOHEX2

MOV DATANOHEX2,A

MOV A,DATAS5

SWAP A

ANL A,#\$F0

MOV DATANOHEX3,A

MOV A,DATAS6

ANL A,#\$0F

ORL A,DATANOHEX3

MOV DATANOHEX3,A

MOV A,DATAS7

SWAP A

ANL A,#\$F0

MOV DATANOHEX4,A

MOV A,DATAS8

ANL A,#\$0F

ORL A,DATANOHEX4

MOV DATANOHEX4,A

## LCALL HEXTODES

MOV A,DATADECHASIL1

LCALL ANDF0

MOV DATANOMORASCII1,A

MOV A,DATADECHASIL1

LCALL AND0F

MOV DATANOMORASCII2,A

MOV A,DATADECHASIL2

LCALL ANDF0

MOV DATANOMORASCII3,A

MOV A,DATADECHASIL2

LCALL AND0F

MOV DATANOMORASCII4,A

MOV A,DATADECHASIL3

LCALL ANDF0

MOV DATANOMORASCII5,A

MOV A,DATADECHASIL3

LCALL AND0F

MOV DATANOMORASCII6,A

MOV A,DATADECHASIL4

LCALL ANDF0

MOV DATANOMORASCII7,A

MOV A, DATADECHASIL4

LCALL AND0F

MOV DATANOMORASCII8,A

MOV A,DATADECHASIL5

LCALL ANDF0

MOV DATANOMORASCII9,A

MOV A,DATADECHASIL5

LCALL AND0F

MOV DATANOMORASCII10,A

MOV STKIRIM,#1

CLR LED

LCALL DELAY

SETB LED

LCALL DELAY

CLR LED

LCALL DELAY

SETB LED

LCALL DELAY

## ;ADA DATA;

CLR LED

SETB KODE

MOV R0,#DATANOMORASCII1

MOV R1,#11

## KIRIMLAGI:

MOV A,@R0

MOV DATAKIRIM,A

LCALL KIRIMKEPC

INC R0

DJNZ R1,KIRIMLAGI

```

SETB LED

```

MOV STKIRIM,#0

**RET**

## KIRIMKEPC:

TG1: JB SS,TG1

MOV A,DATAKIRIM

MOV P1,A

TG2: JB SS,TG2

MOV A,DATAKIRIM

RL A

RL A

RL A

RL A

ANL A,#\$F0

MOV P1,A

LCALL DELAYKIRIM

**RET**

ANDF0: SWAP A

ANL A,#\$0F

ADD A,#\$30

RET

AND0F:

ANL A,#\$0F

ADD A,#\$30

RET

## CEKA\_F:

CEKA: CJNE A,#'A',CEKB

MOV A,#\$0A

ADD A,#\$30

**RET**

CEKB: CJNE A,#'B',CEKC

MOV A,#\$0B

ADD A,#\$30

**RET**

CEKC: CJNE A,#'C',CEKD

MOV A,#\$0C

ADD A,#\$30

**RET**

CEKD: CJNE A,#'D',CEKE

MOV A,#\$0D

ADD A,#\$30

RET

CEKE: CJNE A,#'E',CEKF

MOV A,#\$0E

ADD A,#\$30

RET

CEKF: CJNE A,#'F',CEKPA

MOV A,#\$0F

ADD A,#\$30

CEKPA:

**RET**

## **HEXTODES:**

MOV DATADECHASIL1,#0

MOV DATADECHASIL2,#0

MOV DATADECHASIL3,#0

MOV DATADECHASIL4,#0

MOV DATADECHASIL5,#0

MOV A,DATANOHEX4

KE1: CLR C

RRC A

JNC KE2

LCALL HITBIT1

LCALL HITUNG

KE2: CLR C

RRC A

JNC KE3

LCALL HITBIT2

LCALL HITUNG

KE3: CLR C

RRC A

JNC KE4

LCALL HITBIT3

LCALL HITUNG

KE4: CLR C

RRC A

JNC KE5

LCALL HITBIT4

LCALL HITUNG

KE5: CLR C

RRC A

JNC KE6

LCALL HITBIT5

LCALL HITUNG

KE6: CLR C

RRC A

JNC KE7

LCALL HITBIT6

LCALL HITUNG

KE7: CLR C

RRC A

JNC KE8

LCALL HITBIT7

LCALL HITUNG

KE8: CLR C

RRC A

JNC KE9

LCALL HITBIT8

## LCALL HITUNG

KE9:

MOV A,DATANOHEX3

CLR C

RRC A

JNC KE10

LCALL HITBIT9

LCALL HITUNG

KE10: CLR C

RRC A

JNC KE11

LCALL HITBIT10

LCALL HITUNG

KE11: CLR C

RRC A

JNC KE12

LCALL HITBIT11

LCALL HITUNG

KE12: CLR C

RRC A

JNC KE13

LCALL HITBIT12

LCALL HITUNG

KE13: CLR C

RRC A

JNC KE14

LCALL HITBIT13

LCALL HITUNG

KE14: CLR C

RRC A

JNC KE15

LCALL HITBIT14

LCALL HITUNG

KE15: CLR C

```

RRC A

```

JNC KE16

LCALL HITBIT15

LCALL HITUNG

KE16: CLR C

RRC A

JNC KE17

LCALL HITBIT16

LCALL HITUNG

KE17:

MOV A,DATANOHEX2

CLR C

RRC A

JNC KE18

LCALL HITBIT17

LCALL HITUNG

KE18: CLR C

RRC A

JNC KE19

LCALL HITBIT18

LCALL HITUNG

KE19: CLR C

RRC A

JNC KE20

LCALL HITBIT19

LCALL HITUNG

KE20: CLR C

RRC A

JNC KE21

LCALL HITBIT20

LCALL HITUNG

KE21: CLR C

RRC A

JNC KE22

```

LCALL HITBIT21

```

LCALL HITUNG

KE22: CLR C

RRC A

JNC KE23

LCALL HITBIT22

LCALL HITUNG

KE23: CLR C

RRC A

JNC KE24

LCALL HITBIT23

LCALL HITUNG

KE24: CLR C

RRC A

JNC KE25

LCALL HITBIT24

LCALL HITUNG

KE25:

MOV A,DATANOHEX1

CLR C

RRC A

JNC KE26

LCALL HITBIT25

LCALL HITUNG

KE26: CLR C

RRC A

JNC KE27

LCALL HITBIT26

LCALL HITUNG

KE27: CLR C

RRC A

JNC KE28

LCALL HITBIT27

LCALL HITUNG

KE28: CLR C

RRC A

JNC KE29

LCALL HITBIT28

LCALL HITUNG

KE29: CLR C

RRC A

JNC KE30

LCALL HITBIT29

LCALL HITUNG

KE30: CLR C

RRC A

JNC KE31

LCALL HITBIT30

LCALL HITUNG

KE31: CLR C

RRC A

JNC KE32

LCALL HITBIT31

LCALL HITUNG

KE32: CLR C

RRC A

JNC KE33

LCALL HITBIT32

LCALL HITUNG

KE33:

**RET**

HITUNG: PUSH ACC

MOV A,DATADECHASIL5

ADD A,DATAPENAMBAH5

DA A

## MOV DATADECHASIL5,A

MOV A,DATADECHASIL4

ADDC A,DATAPENAMBAH4

DA A

MOV DATADECHASIL4,A

MOV A,DATADECHASIL3

ADDC A,DATAPENAMBAH3

DA A

MOV DATADECHASIL3,A

MOV A,DATADECHASIL2

ADDC A,DATAPENAMBAH2

DA A

MOV DATADECHASIL2,A

MOV A,DATADECHASIL1

ADDC A,DATAPENAMBAH1

DA A

MOV DATADECHASIL1,A

POP ACC

RET

•\_\_\_\_\_

#### HITBIT1:

MOV DATAPENAMBAH5,#\$01

MOV DATAPENAMBAH4,#\$00

MOV DATAPENAMBAH3,#\$00

MOV DATAPENAMBAH2,#\$00

MOV DATAPENAMBAH1,#\$00

RET

#### HITBIT2:

MOV DATAPENAMBAH5,#\$02

MOV DATAPENAMBAH4,#\$00

MOV DATAPENAMBAH3,#\$00

MOV DATAPENAMBAH2,#\$00

MOV DATAPENAMBAH1,#\$00

**RET**

#### HITBIT3:

MOV DATAPENAMBAH5,#\$04

MOV DATAPENAMBAH4,#\$00

MOV DATAPENAMBAH3,#\$00

MOV DATAPENAMBAH2,#\$00

MOV DATAPENAMBAH1,#\$00

**RET**

#### HITBIT4:

MOV DATAPENAMBAH5,#\$08

MOV DATAPENAMBAH4,#\$00

MOV DATAPENAMBAH3,#\$00

MOV DATAPENAMBAH2,#\$00

MOV DATAPENAMBAH1,#\$00

**RET**

#### HITBIT5:

MOV DATAPENAMBAH5,#\$16

MOV DATAPENAMBAH4,#\$00

MOV DATAPENAMBAH3,#\$00

MOV DATAPENAMBAH2,#\$00

MOV DATAPENAMBAH1,#\$00

**RET**

## HITBIT6:

MOV DATAPENAMBAH5,#\$32

MOV DATAPENAMBAH4,#\$00

MOV DATAPENAMBAH3,#\$00

MOV DATAPENAMBAH2,#\$00

MOV DATAPENAMBAH1,#\$00

## **RET**

#### HITBIT7:

MOV DATAPENAMBAH5,#\$64

MOV DATAPENAMBAH4,#\$00

MOV DATAPENAMBAH3,#\$00

MOV DATAPENAMBAH2,#\$00

MOV DATAPENAMBAH1,#\$00

RET

#### HITBIT8:

MOV DATAPENAMBAH5,#\$28

MOV DATAPENAMBAH4,#\$01

MOV DATAPENAMBAH3,#\$00

MOV DATAPENAMBAH2,#\$00

MOV DATAPENAMBAH1,#\$00

**RET**

;-----

#### HITBIT9:

MOV DATAPENAMBAH5,#\$56

MOV DATAPENAMBAH4,#\$02

MOV DATAPENAMBAH3,#\$00

MOV DATAPENAMBAH2,#\$00

MOV DATAPENAMBAH1,#\$00

RET

## HITBIT10:

MOV DATAPENAMBAH5,#\$12

MOV DATAPENAMBAH4,#\$05

MOV DATAPENAMBAH3,#\$00

MOV DATAPENAMBAH2,#\$00

MOV DATAPENAMBAH1,#\$00

**RET**

## HITBIT11:

MOV DATAPENAMBAH5,#\$24

MOV DATAPENAMBAH4,#\$10 MOV DATAPENAMBAH3,#\$00 MOV DATAPENAMBAH2,#\$00 MOV DATAPENAMBAH1,#\$00 **RET** HITBIT12: DATAPENAMBAH5,#\$48 MOV MOV DATAPENAMBAH4,#\$20 MOV DATAPENAMBAH3,#\$00 MOV DATAPENAMBAH2,#\$00 MOV DATAPENAMBAH1,#\$00 **RET** HITBIT13: MOV DATAPENAMBAH5,#\$96 MOV DATAPENAMBAH4,#\$40 MOV DATAPENAMBAH3,#\$00 MOV DATAPENAMBAH2,#\$00 MOV DATAPENAMBAH1,#\$00 **RET** HITBIT14: MOV DATAPENAMBAH5,#\$92 MOV DATAPENAMBAH4,#\$81 MOV DATAPENAMBAH3,#\$00 MOV DATAPENAMBAH2,#\$00 MOV DATAPENAMBAH1,#\$00 **RET** HITBIT15: MOV DATAPENAMBAH5,#\$84 MOV DATAPENAMBAH4,#\$63 MOV DATAPENAMBAH3,#\$01 MOV DATAPENAMBAH2,#\$00

DATAPENAMBAH1,#\$00

MOV

**RET**

#### HITBIT16:

MOV DATAPENAMBAH5,#\$68

MOV DATAPENAMBAH4,#\$27

MOV DATAPENAMBAH3,#\$03

MOV DATAPENAMBAH2,#\$00

MOV DATAPENAMBAH1,#\$00

RET

;-----

#### HITBIT17:

MOV DATAPENAMBAH5,#\$36

MOV DATAPENAMBAH4,#\$55

MOV DATAPENAMBAH3,#\$06

MOV DATAPENAMBAH2,#\$00

MOV DATAPENAMBAH1,#\$00

RET

#### HITBIT18:

MOV DATAPENAMBAH5,#\$72

MOV DATAPENAMBAH4,#\$10

MOV DATAPENAMBAH3,#\$13

MOV DATAPENAMBAH2,#\$00

MOV DATAPENAMBAH1,#\$00

**RET**

#### HITBIT19:

MOV DATAPENAMBAH5,#\$44

MOV DATAPENAMBAH4,#\$21

MOV DATAPENAMBAH3,#\$26

MOV DATAPENAMBAH2,#\$00

MOV DATAPENAMBAH1,#\$00

**RET**

#### HITBIT20:

MOV DATAPENAMBAH5,#\$88

MOV DATAPENAMBAH4,#\$42

MOV DATAPENAMBAH3,#\$52

MOV DATAPENAMBAH2,#\$00 MOV DATAPENAMBAH1,#\$00 **RET** HITBIT21: MOV DATAPENAMBAH5,#\$76 MOV DATAPENAMBAH4,#\$85 MOV DATAPENAMBAH3,#\$04 MOV DATAPENAMBAH2,#\$01 MOV DATAPENAMBAH1,#\$00 **RET** HITBIT22: MOV DATAPENAMBAH5,#\$52 MOV DATAPENAMBAH4,#\$71 MOV DATAPENAMBAH3,#\$09 MOV DATAPENAMBAH2,#\$02 MOV DATAPENAMBAH1,#\$00 RET HITBIT23: MOV DATAPENAMBAH5,#\$04 MOV DATAPENAMBAH4,#\$43 MOV DATAPENAMBAH3,#\$19 MOV DATAPENAMBAH2,#\$04 MOV DATAPENAMBAH1,#\$00 RET HITBIT24: MOV DATAPENAMBAH5,#\$08 MOV DATAPENAMBAH4,#\$86 DATAPENAMBAH3,#\$38 MOV MOV DATAPENAMBAH2,#\$08 MOV DATAPENAMBAH1,#\$00 **RET**

HITBIT25:

MOV DATAPENAMBAH5,#\$16

## MOV DATAPENAMBAH4,#\$72 MOV DATAPENAMBAH3,#\$77 MOV DATAPENAMBAH2,#\$16 MOV DATAPENAMBAH1,#\$00 **RET** HITBIT26: MOV DATAPENAMBAH5,#\$32 MOV DATAPENAMBAH4,#\$44 MOV DATAPENAMBAH3,#\$55 MOV DATAPENAMBAH2,#\$33 MOV DATAPENAMBAH1,#\$00 RET HITBIT27: MOV DATAPENAMBAH5,#\$64 MOV DATAPENAMBAH4,#\$88 MOV DATAPENAMBAH3,#\$10 MOV DATAPENAMBAH2,#\$67 MOV DATAPENAMBAH1,#\$00 **RET** HITBIT28: MOV DATAPENAMBAH5,#\$28 MOV DATAPENAMBAH4,#\$77 MOV DATAPENAMBAH3,#\$21 MOV DATAPENAMBAH2,#\$34 MOV DATAPENAMBAH1,#\$01 **RET** HITBIT29: MOV DATAPENAMBAH5,#\$56 MOV DATAPENAMBAH4,#\$54 MOV DATAPENAMBAH3,#\$43 MOV DATAPENAMBAH2,#\$68 MOV DATAPENAMBAH1,#\$02 **RET**

HITBIT30:

## MOV DATAPENAMBAH5,#\$12

MOV DATAPENAMBAH4,#\$09

MOV DATAPENAMBAH3,#\$87

MOV DATAPENAMBAH2,#\$36

MOV DATAPENAMBAH1,#\$05

**RET**

## HITBIT31:

MOV DATAPENAMBAH5,#\$24

MOV DATAPENAMBAH4,#\$18

MOV DATAPENAMBAH3,#\$74

MOV DATAPENAMBAH2,#\$73

MOV DATAPENAMBAH1,#\$10

RET

#### HITBIT32:

MOV DATAPENAMBAH5,#\$48

MOV DATAPENAMBAH4,#\$36

MOV DATAPENAMBAH3,#\$48

MOV DATAPENAMBAH2,#\$47

MOV DATAPENAMBAH1,#\$21

**RET**

:------

## INITSERIAL:

MOV TMOD,#20H

MOV TCON,#41H

MOV TH1,#0FDH

MOV SCON,#50H

**RET**

DELAY: MOV R5,#\$01

DELAY1: MOV R6,#\$FF

DELAY2: MOV R7,#\$FF

DELAY3: DJNZ R7,DELAY3

DJNZ R6,DELAY2

DJNZ R5,DELAY1

DELAYKIRIM:

MOV R6,#\$01

DELAYK1: MOV R7,#\$FF

DELAYK2: DJNZ R7,DELAYK2

DJNZ R6,DELAYK1

RET

.END

```

unit FUnit1;

interface

uses

Windows, Messages, SysUtils, Variants, Classes, Graphics, Controls, Forms,

Dialogs, StdCtrls, Buttons, ExtCtrls;

type

Tfutama = class(TForm)

pjam: TPanel;

ptanggal: TPanel;

BitBtn1: TBitBtn;

BitBtn2: TBitBtn;

BitBtn3: TBitBtn;

Panel1: TPanel;

Label1: TLabel;

Pnamamasuk: TPanel;

Pkartumasuk: TPanel;

Timer1: TTimer;

procedure BitBtn1Click(Sender: TObject);

procedure Timer1Timer(Sender: TObject);

procedure BitBtn2Click(Sender: TObject);

procedure FormCreate(Sender: TObject);

private

{ Private declarations }

public

{ Public declarations }

end;

var

futama: Tfutama;

databaca,datal1,datah1,databacaH,databacaL:integer;

datal,datah:byte;

```

```

datakartu:string;

datas1,

datas2,

datas3,

datas4,

datas5,

datas6,

datas7,

datas8,

datas9,

datas10:string;

datab1,

datab2,

datab3,

datab4,

datab5,

datab6,

datab7,

datab8,

datab9,

datab10:byte;

datastatus:byte;

datakartumasuk:string;

stketemu:boolean;

Nama, Nomor Kartu: string;

implementation

uses Unittambahdata, unitbrowse;

{$R *.dfm}

procedure Tfutama.BitBtn1Click(Sender: TObject);

begin

Ftambahdata.show;

end;

```

```

procedure WritePortInit;

begin

asm

dx,$37a;

mov

al,$04;

mov

out

dx,al

end;

end;

procedure WritePortHigh;

begin

asm

dx,$378;

mov

al,$03;

mov

dx,al

out

end;

end;

procedure WritePortLow;

begin

asm

dx,$378;

mov

al,$00;

mov

dx,al;

out

end;

end;

procedure bacaportLow;

begin

asm

mov dx,$37a;

in al,dx;

mov datal, al;

end;

datal:=datal and $0f;

end;

```

```

procedure bacaportHigh;

begin

asm

mov dx,$379;

in al,dx;

mov datah,al;

end;

datastatus:=datah and $08;

datah:=(datah shr 4) and $0f;

end;

procedure Tfutama.Timer1Timer(Sender: TObject);

var delay1,delay2:longint;

code:integer;

begin

pjam.caption:=formatdatetime('hh:mm:ss',time);

ptanggal.caption:=formatdatetime('dd/mm/yyyy',date);

bacaportHigh;

if datastatus=$08 then

begin

writeportlow;

bacaportHIGH;

writeporthigh;

databacah:=datah;

writeportlow;

bacaporthigh;

writeporthigh;

databacal:=datah;

databaca:=databacah+databacal;

if (databacah=$0f) or (databacal=$0f) then databaca:=0;

```

```

if ((databacah<>$0f) and (databacal<>$0f)) then

begin

datakartumasuk:=datakartumasuk+inttostr(databacah)+inttostr(databacal);

{ pkartumasuk.caption:=datakartumasuk;}

if length(datakartumasuk)=23 then

begin

datakartu:=copy(datakartumasuk,3,20);

datas1:=copy(datakartu,1,2);

datas2:=copy(datakartu,3,2);

datas3:=copy(datakartu,5,2);

datas4:=copy(datakartu,7,2);

datas5:=copy(datakartu,9,2);

datas6:=copy(datakartu,11,2);

datas7:=copy(datakartu,13,2);

datas8:=copy(datakartu,15,2);

datas9:=copy(datakartu,17,2);

datas10:=copy(datakartu,19,2);

val('$'+datas1,datab1,code);

val('$'+datas2,datab2,code);

val('$'+datas3,datab3,code);

val('$'+datas4,datab4,code);

val('$'+datas5,datab5,code);

val('$'+datas6,datab6,code);

val('$'+datas7,datab7,code);

val('$'+datas8,datab8,code);

val('$'+datas9,datab9,code);

val('$'+datas10,datab10,code);

datakartu:=chr(datab1)+chr(datab2)+chr(datab3)+chr(datab4)+chr(datab5)+chr(datab

6)+chr(datab7)+chr(datab8)+chr(datab9)+chr(datab10);

pkartumasuk.caption:=datakartu;

```

```

with ftambahdata do

begin

tablekaryawan.first;

tablekaryawan.refresh;

stketemu:=false;

while not tablekaryawan.eof do

begin

if tablekaryawan.fieldbyname('NOMORKARTU').asstring=datakartu then

begin

stketemu:=true;

nama:=tablekaryawan.fieldbyname('NAMA').asstring;

nomork artu:= table karyawan. field by name ('NOMORKARTU'). asstring;\\

tablekaryawan.last;

end;

tablekaryawan.next;

end;

end;

if stketemu then

begin

pnamamasuk.caption:=nama;

with fbrowsedata do

begin

tabledata.refresh;

tabledata.last:

tabledata.insert;

tabledata.fieldbyname('TANGGAL').asstring:=ptanggal.caption;

tabledata.fieldbyname('JAM').asstring:=pjam.caption;

tabledata.fieldbyname('NAMA').asstring:=nama;

tabledata.fieldbyname('NO_KARTU').asstring:=nomorkartu;

tabledata.refresh;

end;

```

```

end else

begin

pnamamasuk.caption:='TIDAK ADA';

pkartumasuk.caption:=";

end;

datakartumasuk:=";

databaca:=0;

end;

end;

\{CAPTION := INTTOSTR(DATAbacaH) + ' + INTTOSTR(DATAbacaI); \}

end;

end;

procedure Tfutama.BitBtn2Click(Sender: TObject);

begin

fbrowsedata.show;

end;

procedure Tfutama.FormCreate(Sender: TObject);

begin

stketemu:=false;

datakartumasuk:=";

timer1.interval:=10;

asm

mov dx,$37a;

in al,dx;

mov datal, al;

end;

datal:=((datal and $f0) or $04);

```

```

asm

mov dx,$37a;

mov al,datal;

out dx,al;

end;

writeporthigh;

end;

```

end.

## LAMPIRAN B DATA KOMPONEN KARTU

## **Contactless Card Specification**

| Model No.                           | ISO Card                        | Imm ISO Card                       | Clamshell Card                      |

|-------------------------------------|---------------------------------|------------------------------------|-------------------------------------|

| Reading Distance                    | 80mm                            | 100mm                              | I 60mm                              |

| Base on GK4001 chip, with EM9917 R  | eader                           |                                    |                                     |

| Operating temperature               | -20°C to 50°C                   | -20°C to 50°C                      | -20°C to 70°C                       |

| Storage temperature                 | -20°C to 50°C                   | -20°C to 50°C                      | -40°C to 80°C                       |

| Material                            | PVC/PET                         | PVC                                | ABS                                 |

| Operating Frequency                 | 125KHz / 13.56MHz               | 125KHz                             | 125KHz / 13.56MHz                   |

| Antenna                             | Copper Coil                     | Copper Coil                        | Copper Coil                         |

| Dimensions 85.6m                    | m+0.12×53.98mm+0.05×0.76mm+0.08 | 85.6mm+0.12x53.98mm+0.05x10mm+0.08 | 85.6mm+0.12x53.98mm+0.05x1.84mm+0.0 |

| Technology                          |                                 |                                    |                                     |

| GK4001 (125KHz, 64bit, R/O)         | Υ                               | Υ                                  | Υ                                   |

| H4102 (125KHz, 64bit, R/O)          | Y                               | Y                                  | Υ                                   |

| I-Code SLI (13.56MHz, 1024bit, R/W) | Y                               | Υ                                  | Y                                   |

| Mifare S50 (13.56MHz, 1KByte, R/W)  | Y                               | Υ                                  | Y                                   |

| Temic E5557 (125KHz, 330bit, R/W)   | Y                               | Υ                                  | Y                                   |

| Hitag I (125KHz, 2048bit, R/W)      | Y                               | Υ                                  | Y                                   |

| Hitag 2 (125KHz, 256bit, R/W)       | Υ                               | Υ                                  | Υ                                   |

| Legic 256 (13.56MHz, 256Byte, R/W)  | Y                               | Y                                  | Y                                   |

Application: Door Access Control, Burglar Prevention, Patrol Management, Personal Identification, Car Park Control, Member Club Management, etc.

# LAMPIRAN C DATA KOMPONEN READER

# ID-2, ID-12, ID-20

(includingID-0, ID-10, ID-15)

Reader Specification

Low Cost – Short Range RFID Compact Reader Modules

Advanced Reader Development

Advanced Digital Reader Technology

Manual Rev 0.2

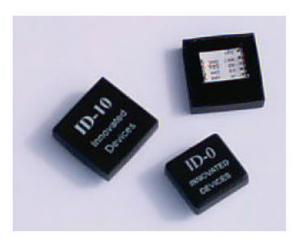

### PRODUCT DESCRIPTION

The ID-2, ID-12 and ID-20 are hybrid RFID reader modules that provide simple, consistent and flexible implementation of this technology into existing swipe card based ID equipment.

With the simple addition of an antenna and a capacitor to suit your specific design and needs, equipment such as access control units, time and attendance equipment or workstation logging equipment can be converted to the popular wireless ID designs.

The ID-2, ID-12 and ID-20 are readers for the popular EM4001 format 125KHz tags. Read ranges of 115 cm are possible with ISO cards (25cm with a well tuned matched antenna on the ID-2). With CMOS/TTL Serial, Wiegand26 and NEW with this series, Magnetic ABA Track 2 format, swipe cards can be emulated. Furthermore, the readers are encapsulated for environmental protection and potential damage or changes during manufacture or handling.

The ID-2 requires an external antenna, ideal for custom cased installations. The ID-12 & ID-20 has an internal antenna, allowing fast integration, particularly when space is a premium.

# ANTENNA DESIGN

Maximum coil sizes:-

ISO Card - 15cm x 15cm for ISO Card Glass Tag - 10cm x 10cm for Glass Tag

# ANTENNA DESIGN PRINCIPLES

- Generally the bigger the antenna the better, as long as there is enough field strength to excite the tag.

- It is possible to calculate the optimum size of an antenna, but there is always an element of try it

and see.

### Elements affecting reading range.

- In areas of interference reduction in reading range is unavoidable.

- Reducing the coil size will provide more concentrated field strength and coupling.

### Choice Of Tuning Capacitor

Quality of capacitor can significantly affect the quality of your system. For quality and reliability we recommend the following capacitor types:-

- Polypropylene

- COG/NPO

- Polyethylene Sulfide

- Mica

- Polycarbonate

Capacitors rated voltage (MUST cope with RMS voltage at 125kHz). It is recommend starting with 630v 1n5 Polypropylene. After experimentation, the voltage and capacitor type can come down to measured values. Do not go by DC voltage rating. The tolerance should be 2% preferred, 5% acceptable.

### ANTENNA DESIGN STEPS

- If antenna design is governed by enclosure size and is less than 4cmx4cm, wind the coil to 640uH and skip steps 2-4.

- 2. If target transducer is small, do not wind the coil more than 10cmx10cm

- In heavy interference, start with a large coil and reduce the size to see if there is significant improvement.

- 4. If there is a large mass of metal in proximity, the inductance will be changed, usually reducing the original value. Start with a higher inductance. Using a smaller coil may help, by increasing the field strength and coupling.

- The ID-2 has a maximum current allowed of 200mA. Corresponding to 100v Pk to Pk.If the antenna voltage is higher, the designer can risk it or lower the Q by adding a series resistor in the coil.

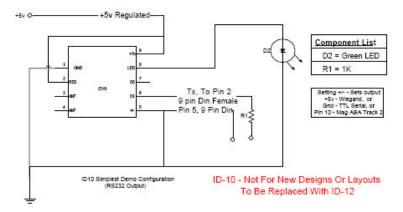

# EXAMPLE CIRCUITS

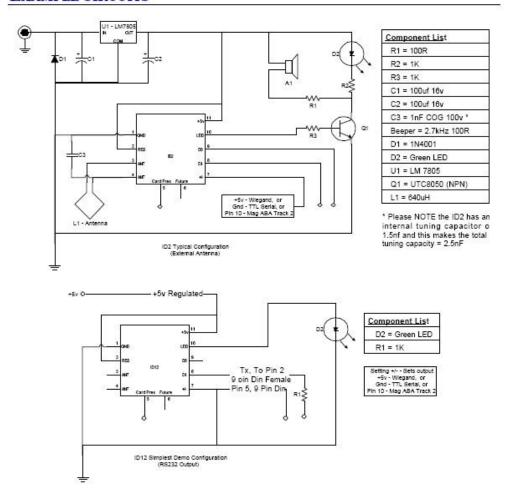

# PIN LAYOUTS AND SPACING

Please note, the pin layouts and spacing are the same for the modules, the casing sizes differ to allow for internal antennas where applicable.

# SPECIFICATIONS ID-2, ID-12, ID-20

### Low Cost Short-Range Proximity Readers

The ID Series short-range readers come in three different sizes and read ranges. The ID-12 and ID-20 come with internal antennas, and have read ranges of 12+ cm and 16+ cm, respectively. With an external antenna, the ID-2 can deliver read ranges of up to 25 cm. All three readers support ASCII, Wiegand26 and Magnetic ABA Track2 data formats.

# Operational and Physical Characteristics

| Parameters           | ID-2                          | ID-12                         | ID-20                         |

|----------------------|-------------------------------|-------------------------------|-------------------------------|

| Read Range           | N/A (no internal antenna)     | 12+ cm                        | 15+ cm                        |

| Dimensions           | 21 mm x 19 mm x 6 mm          | 26 mm x 25 mm x 7 mm          | 40 mm x 40 mm x 9 mm          |

| Frequency            | 125 kHz                       | 125 kHz                       | 125 kHz                       |

| Card Format          | EM 4001 or compatible         | EM 4001 or compatible         | EM 4001 or compatible         |

| Encoding             | Manchester 64-bit, modulus 64 | Manchester 64-bit, modulus 64 | Manchester 64-bit, modulus 64 |

| Power Requirement    | 5 VDC @ 13mA nominal          | 5 VDC @ 30mA nominal          | 5 VDC @ 55mA nominal          |

| I/O Output Current   | +/-200mA PK                   | 12 <sup>2</sup> 3             | 12 <del>1</del> 2             |

| Voltage Supply Range | +4.6V through +5.4V           | +4.6V through +5.4V           | +4.6V through +5.4V           |

# Pin Description & Output Data Formats

| Pin<br>No. | Description                                 | ASCII               | Magnet Emulation | Wiegand26    |

|------------|---------------------------------------------|---------------------|------------------|--------------|

| Pin 1      | Zero Volts and Tuning Capacitor<br>Ground   | GND 0V              | GND 0V           | GND 0V       |

| Pin 2      | Strap to +5V                                | Reset Bar           | Reset Bar        | Reset Bar    |

| Pin 3      | To External Antenna and Tuning<br>Capacitor | Antenna             | Antenna          | Antenna      |

| Pin 4      | To External Antenna                         | Antenna             | Antenna          | Antenna      |

| Pin 5      | Card Present                                | No function         | Card Present     | No function  |

| Pin 6      | Future                                      | Future              | Future           | Future       |

| Pin 7      | Format Selector (+/-)                       | Strap to GND        | Strap to Pin 10  | Strap to +5V |

| Pin 8      | Data 1                                      | CMOS                | Data             | One Output   |

| Pin 9      | Data 0                                      | TTL Data (inverted) | Clock            | Zero Output  |

| Pin 10     | 2.7 kHz Logic                               | Beeper / LED        | Beeper / LED     | Beeper / LED |

| Pin 11     | DC Voltage Supply                           | +5V                 | +5V              | +5V          |

# SPECIFICATIONS ID-0, ID-10, ID-15 (NOT FOR NEW DESIGNS)

# Low Cost Short-Range Proximity Readers

The ID Series short-range readers come in three different sizes and read ranges. Both the ID-10 and ID-15 come with internal antennas, and have read ranges of 12+ cm and 16+ cm, respectively. With an external antenna, the ID-0 Mk(ii) can deliver read ranges of up to 25 cm. All three readers support ASCII and Wiegand26 data formats.

Manual # ID2-181002-0.0

# Operational and Physical Characteristics

| Parameters           | ID-0                          | ID-10                         | ID-15                         |

|----------------------|-------------------------------|-------------------------------|-------------------------------|

| Read Range           | N/A (no internal antenna)     | 12+ cm                        | 15+ cm                        |

| Dimensions           | 21 mm x 19 mm x 6 mm          | 26 mm x 25 mm x 7 mm          | 40 mm x 40 mm x 9 mm          |

| Frequency            | 125 kHz                       | 125 kHz                       | 125 kHz                       |

| Card Format          | EM 4001 or compatible         | EM 4001 or compatible         | EM 4001 or compatible         |

| Encoding             | Manchester 64-bit, modulus 64 | Manchester 64-bit, modulus 64 | Manchester 64-bit, modulus 64 |

| Power Requirement    | 5 VDC @ 13mA nominal          | 5 VDC @ 30mA nominal          | 5 VDC @ 50mA nominal          |

| I/O Output Current   | +/-200mA PK                   |                               |                               |

| Voltage Supply Range | +4.6V through +5.4V           | +4.6V through +5.4V           | +4.6V through +5.4V           |

# Pin Description & Output Data Formats

| Pin No. | Description                              | ASCII               | Wiegand26    |

|---------|------------------------------------------|---------------------|--------------|

| Pin 1   | Zero Volts and Tuning Capacitor Ground   | GND 0V              | GND 0V       |

| Pin 2   | Strap to +5V                             | Reset Bar           | Reset Bar    |

| Pin 3   | To External Antenna and Tuning Capacitor | Antenna             | Antenna      |

| Pin 4   | To External Antenna                      | Antenna             | Antenna      |

| Pin 5   | Format Selector (+/-)                    | Strap to GND        | Strap to +5V |

| Pin 6   | Data 1                                   | CMOS                | One Output   |

| Pin 7   | Data 0                                   | TTL Data (inverted) | Zero Output  |

| Pin 8   | 2.7 kHz Logic                            | Beeper / LED        | Beeper / LED |

| Pin 9   | DC Voltage Supply                        | +5V                 | +5V          |

# **EXAMPLE CIRCUITS**

# **DATA FORMATS**

### Output Data Structure - ASCII (TTL Level RS2323)

| STX (02h)                  | DATA (10 ASCII)                   | CHECKSUM                 | CR          | LF | ETX (03h) |

|----------------------------|-----------------------------------|--------------------------|-------------|----|-----------|

| The checksum is the result | t of the XOR of the 5 binary Data | bytes (the 10 ASCII data | characters) |    | •         |

# Output Data Structure - Wiegand26

| 1      | 2 | 3 | 4 | 5 | 6   | 7    | 8     | 9   | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19    | 20    | 21   | 22 | 23 | 24 | 25 | 26 |

|--------|---|---|---|---|-----|------|-------|-----|----|----|----|----|----|----|----|----|----|-------|-------|------|----|----|----|----|----|

| P      | Ε | Ε | Ε | Е | Е   | Ε    | Ε     | Ε   | Ε  | Ε  | Ε  | Ε  | 0  | 0  | 0  | 0  | 0  | 0     | 0     | 0    | 0  | 0  | 0  | 0  | P  |

| ).<br> |   |   |   | Е | ven | pari | ty (E | (3) |    |    |    |    |    |    |    |    | C  | )dd j | parit | y (O | )  |    |    |    |    |

P = Parity start bit and stop bit

Specifications subject to change. ARD reserves the right to change its products and the specifications given here at any time without notice.

Advanced Reader Developments

Advanced Digital Reader Technology

For OEM and Technical Support Please Contact

Mannings-RFID, Units 1-5 Russell Road, Southport, Merseyside, PR9 7RJ Tel: +44 1704 539000, EMail: Sandra@mannings.uk.com

Advanced Reader Developments

Page 8 of 8

ID-0 & ID-10

# LAMPIRAN D DATA KOMPONEN MIKRO AT89C51

### **Features**

- Compatible with MCS-51<sup>™</sup> Products

- 4K Bytes of In-System Reprogrammable Flash Memory

- Endurance: 1,000 Write/Erase Cycles

- · Fully Static Operation: 0 Hz to 24 MHz

- · Three-level Program Memory Lock

- 128 x 8-bit Internal RAM

- 32 Programmable I/O Lines

- . Two 16-bit Timer/Counters

- · Six Interrupt Sources

- · Programmable Serial Channel

- Low-power Idle and Power-down Modes

# Description

The AT89C51 is a low-power, high-performance CMOS 8-bit microcomputer with 4K bytes of Flash programmable and erasable read only memory (PEROM). The device is manufactured using Atmel's high-density nonvolatile memory technology and is compatible with the industry-standard MCS-51 instruction set and pinout. The on-chip Flash allows the program memory to be reprogrammed in-system or by a conventional nonvolatile memory programmer. By combining a versatile 8-bit CPU with Flash on a monolithic chip, the Atmel AT89C51 is a powerful microcomputer which provides a highly-flexible and cost-effective solution to many embedded control applications.

# 8-bit Microcontroller with 4K Bytes Flash

# AT89C51

Not Recommended for New Designs. Use AT89S51.

Rev. 0265G-02/00

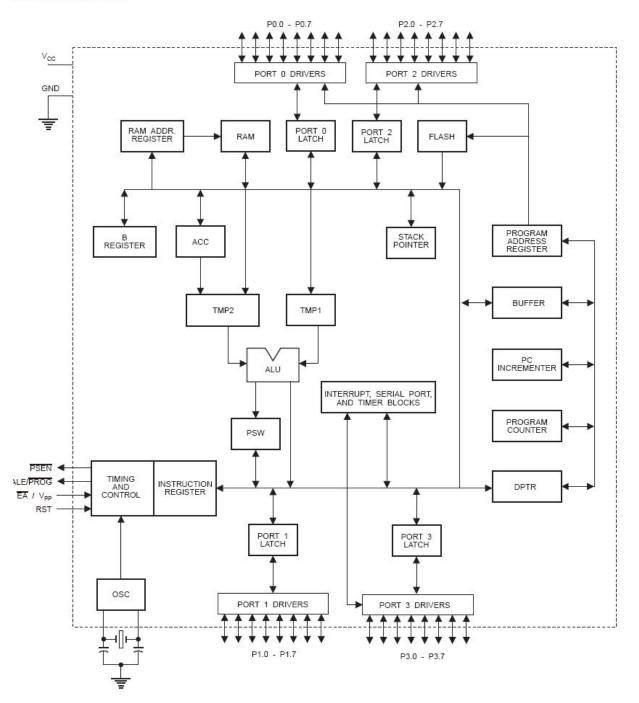

# **Block Diagram**

The AT89C51 provides the following standard features: 4K bytes of Flash, 128 bytes of RAM, 32 I/O lines, two 16-bit timer/counters, a five vector two-level interrupt architecture, a full duplex serial port, on-chip oscillator and clock circuitry. In addition, the AT89C51 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port and interrupt system to continue functioning. The Power-down Mode saves the RAM contents but freezes the oscillator disabling all other chip functions until the next hardware reset.

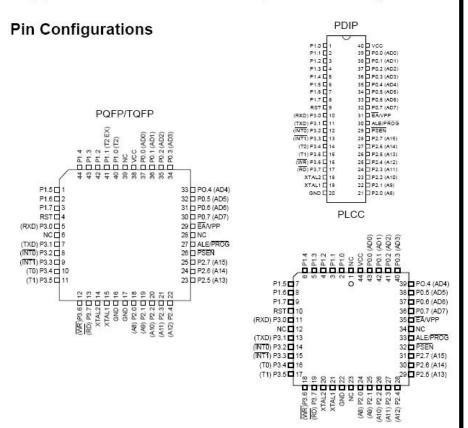

# **Pin Description**

### VCC

Supply voltage.

### GND

Ground.

### Port 0

Port 0 is an 8-bit open-drain bi-directional I/O port. As an output port, each pin can sink eight TTL inputs. When 1s are written to port 0 pins, the pins can be used as high-impedance inputs.

Port 0 may also be configured to be the multiplexed loworder address/data bus during accesses to external program and data memory. In this mode P0 has internal pullups.

Port 0 also receives the code bytes during Flash programming, and outputs the code bytes during program verification. External pullups are required during program verification.

### Port 1

Port 1 is an 8-bit bi-directional I/O port with internal pullups. The Port 1 output buffers can sink/source four TTL inputs. When 1s are written to Port 1 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current ( $I_{\parallel}$ ) because of the internal pullups.

Port 1 also receives the low-order address bytes during Flash programming and verification.

### Port 2

Port 2 is an 8-bit bi-directional I/O port with internal pullups. The Port 2 output buffers can sink/source four TTL inputs. When 1s are written to Port 2 pins they are pulled high by the internal pullups and can be used as inputs. As inputs,

Port 2 pins that are externally being pulled low will source current ( $I_{IL}$ ) because of the internal pullups.

Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @ DPTR). In this application, it uses strong internal pullups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @ RI), Port 2 emits the contents of the P2 Special Function Register.

Port 2 also receives the high-order address bits and some control signals during Flash programming and verification.

### Port 3

Port 3 is an 8-bit bi-directional I/O port with internal pullups. The Port 3 output buffers can sink/source four TTL inputs. When 1s are written to Port 3 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current ( $I_{\rm IL}$ ) because of the pullups.

Port 3 also serves the functions of various special features of the AT89C51 as listed below:

| Port Pin | Alternate Functions                    |

|----------|----------------------------------------|

| P3.0     | RXD (serial input port)                |

| P3.1     | TXD (serial output port)               |

| P3.2     | INT0 (external interrupt 0)            |

| P3.3     | INT1 (external interrupt 1)            |

| P3.4     | T0 (timer 0 external input)            |

| P3.5     | T1 (timer 1 external input)            |

| P3.6     | WR (external data memory write strobe) |

| P3.7     | RD (external data memory read strobe)  |

Port 3 also receives some control signals for Flash programming and verification.

### RST

Reset input. A high on this pin for two machine cycles while the oscillator is running resets the device.

### ALE/PROG

Address Latch Enable output pulse for latching the low byte of the address during accesses to external memory. This pin is also the program pulse input (PROG) during Flash programming.

In normal operation ALE is emitted at a constant rate of 1/6 the oscillator frequency, and may be used for external timing or clocking purposes. Note, however, that one ALE

pulse is skipped during each access to external Data Memory.

If desired, ALE operation can be disabled by setting bit 0 of SFR location 8EH. With the bit set, ALE is active only during a MOVX or MOVC instruction. Otherwise, the pin is weakly pulled high. Setting the ALE-disable bit has no effect if the microcontroller is in external execution mode.

### **PSEN**

Program Store Enable is the read strobe to external program memory.

When the AT89C51 is executing code from external program memory,  $\overline{\text{PSEN}}$  is activated twice each machine cycle, except that two  $\overline{\text{PSEN}}$  activations are skipped during each access to external data memory.

### EA/VPP

External Access Enable.  $\overline{EA}$  must be strapped to GND in order to enable the device to fetch code from external program memory locations starting at 0000H up to FFFFH. Note, however, that if lock bit 1 is programmed,  $\overline{EA}$  will be internally latched on reset.

$\overline{\text{EA}}$  should be strapped to  $V_{\text{CC}}$  for internal program executions.

This pin also receives the 12-volt programming enable voltage ( $V_{pp}$ ) during Flash programming, for parts that require 12-volt  $V_{pp}$ .

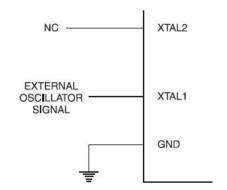

### XTAL1

Input to the inverting oscillator amplifier and input to the internal clock operating circuit.

### XTAL 2

Output from the inverting oscillator amplifier.

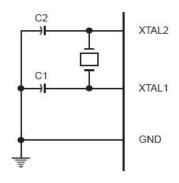

### Oscillator Characteristics

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier which can be configured for use as an on-chip oscillator, as shown in Figure 1. Either a quartz crystal or ceramic resonator may be used. To drive the device from an external clock source. XTAL2 should be left

unconnected while XTAL1 is driven as shown in Figure 2. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is through a divide-by-two flip-flop, but minimum and maximum voltage high and low time specifications must be observed.

## Idle Mode

In idle mode, the CPU puts itself to sleep while all the onchip peripherals remain active. The mode is invoked by software. The content of the on-chip RAM and all the special functions registers remain unchanged during this mode. The idle mode can be terminated by any enabled interrupt or by a hardware reset.

It should be noted that when idle is terminated by a hard ware reset, the device normally resumes program execution, from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write to a port pin when Idle is terminated by reset, the instruction following the one that invokes Idle should not be one that writes to a port pin or to external memory.

Figure 1. Oscillator Connections

Note: C1, C2 = 30 pF ± 10 pF for Crystals = 40 pF ± 10 pF for Ceramic Resonators

# Status of External Pins During Idle and Power-down Modes

| Mode       | Program Memory | ALE | PSEN | PORT0 | PORT1 | PORT2   | PORT3 |

|------------|----------------|-----|------|-------|-------|---------|-------|

| Idle       | Internal       | 1   | 1    | Data  | Data  | Data    | Data  |

| Idle       | External       | 1   | 1    | Float | Data  | Address | Data  |

| Power-down | Internal       | 0   | 0    | Data  | Data  | Data    | Data  |

| Power-down | External       | 0   | 0    | Float | Data  | Data    | Data  |

Figure 2. External Clock Drive Configuration

### Power-down Mode

In the power-down mode, the oscillator is stopped, and the instruction that invokes power-down is the last instruction executed. The on-chip RAM and Special Function Regis-

ters retain their values until the power-down mode is terminated. The only exit from power-down is a hardware reset. Reset redefines the SFRs but does not change the on-chip RAM. The reset should not be activated before  $V_{\rm CC}$  is restored to its normal operating level and must be held active long enough to allow the oscillator to restart and stabilize.

# **Program Memory Lock Bits**

On the chip are three lock bits which can be left unprogrammed (U) or can be programmed (P) to obtain the additional features listed in the table below.

When lock bit 1 is programmed, the logic level at the  $\overline{EA}$  pin is sampled and latched during reset. If the device is powered up without a reset, the latch initializes to a random value, and holds that value until reset is activated. It is necessary that the latched value of  $\overline{EA}$  be in agreement with the current logic level at that pin in order for the device to function properly.

# **Lock Bit Protection Modes**

|   | Program | Lock Bits |     |                                                                                                                                                                                                         |

|---|---------|-----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | LB1     | LB2       | LB3 | Protection Type                                                                                                                                                                                         |

| 1 | U       | Ü         | U   | No program lock features                                                                                                                                                                                |

| 2 | Р       | U         | U   | MOVC instructions executed from external program memory are disabled from fetching code bytes from internal memory, EA is sampled and latched on reset and further programming of the Flash is disabled |

| 3 | Р       | Р         | U   | Same as mode 2, also verify is disabled                                                                                                                                                                 |

| 4 | Р       | Р         | Р   | Same as mode 3, also external execution is disabled                                                                                                                                                     |

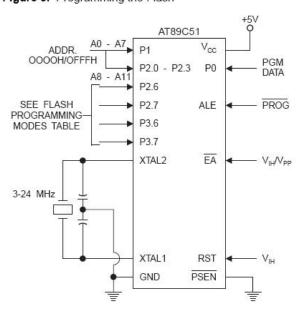

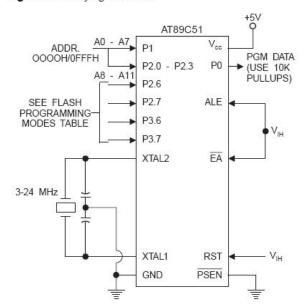

# Programming the Flash

The AT89C51 is normally shipped with the on-chip Flash memory array in the erased state (that is, contents = FFH) and ready to be programmed. The programming interface accepts either a high-voltage (12-volt) or a low-voltage (V<sub>CC</sub>) program enable signal. The low-voltage programming mode provides a convenient way to program the AT89C51 inside the user's system, while the high-voltage programming mode is compatible with conventional third-party Flash or EPROM programmers.

The AT89C51 is shipped with either the high-voltage or low-voltage programming mode enabled. The respective top-side marking and device signature codes are listed in the following table.

|               | V <sub>PP</sub> = 12V                        | V <sub>PP</sub> = 5V                         |

|---------------|----------------------------------------------|----------------------------------------------|

| Top-side Mark | AT89C51<br>xxxx<br>yyww                      | AT89C51<br>xxxx-5<br>yyww                    |

| Signature     | (030H) = 1EH<br>(031H) = 51H<br>(032H) =F FH | (030H) = 1EH<br>(031H) = 51H<br>(032H) = 05H |

The AT89C51 code memory array is programmed byte-bybyte in either programming mode. To program any nonblank byte in the on-chip Flash Memory, the entire memory must be erased using the Chip Erase Mode.

**Programming Algorithm:** Before programming the AT89C51, the address, data and control signals should be set up according to the Flash programming mode table and Figure 3 and Figure 4. To program the AT89C51, take the following steps.

- Input the desired memory location on the address lines.

- 2. Input the appropriate data byte on the data lines.

- 3. Activate the correct combination of control signals.

- Raise EA/V<sub>PP</sub> to 12V for the high-voltage programming mode.

- Pulse ALE/PROG once to program a byte in the Flash array or the lock bits. The byte-write cycle is self-timed and typically takes no more than 1.5 ms. Repeat steps 1 through 5, changing the address

and data for the entire array or until the end of the object file is reached.

Data Polling: The AT89C51 features Data Polling to indicate the end of a write cycle. During a write cycle, an attempted read of the last byte written will result in the complement of the written datum on PO.7. Once the write cycle has been completed, true data are valid on all outputs, and the next cycle may begin. Data Polling may begin any time after a write cycle has been initiated.

Ready/Busy: The progress of byte programming can also be monitored by the RDY/BSY output signal. P3.4 is pulled low after ALE goes high during programming to indicate BUSY. P3.4 is pulled high again when programming is done to indicate READY.

**Program Verify:** If lock bits LB1 and LB2 have not been programmed, the programmed code data can be read back via the address and data lines for verification. The lock bits cannot be verified directly. Verification of the lock bits is achieved by observing that their features are enabled.

**Chip Erase:** The entire Flash array is erased electrically by using the proper combination of control signals and by holding ALE/PROG low for 10 ms. The code array is written with all "1"s. The chip erase operation must be executed before the code memory can be re-programmed.

Reading the Signature Bytes: The signature bytes are read by the same procedure as a normal verification of locations 030H, 031H, and 032H, except that P3.6 and P3.7 must be pulled to a logic low. The values returned are as follows.

(030H) = 1EH indicates manufactured by Atmel

(031H) = 51H indicates 89C51

(032H) = FFH indicates 12V programming (032H) = 05H indicates 5V programming

## Programming Interface

Every code byte in the Flash array can be written and the entire array can be erased by using the appropriate combination of control signals. The write operation cycle is self-timed and once initiated, will automatically time itself to completion.

All major programming vendors offer worldwide support for the Atmel microcontroller series. Please contact your local programming vendor for the appropriate software revision.

# **Flash Programming Modes**

| Mode             |         | RST | PSEN | ALE/PROG | EA/V <sub>PP</sub> | P2.6 | P2.7 | P3.6 | P3.7 |

|------------------|---------|-----|------|----------|--------------------|------|------|------|------|

| Write Code Data  |         | н   | L    | ~~       | H/12V              | L    | Н    | Н    | Н    |

| Read Code Data   |         | Н   | L    | Н        | Н                  | L    | L    | Н    | Н    |

| Write Lock       | Bit - 1 | н   | L,   | ~~       | H/12V              | Н    | Н    | Н    | Н    |

|                  | Bit - 2 | Н   | L    |          | H/12V              | н    | Н    | L    | L    |

|                  | Bit - 3 | Н   | L    | ~        | H/12V              | Н    | L    | Н    | L    |

| Chip Erase       |         | Н   | L    | (1)      | H/12V              | Н    | L    | L    | L    |

| Read Signature B | yte     | Н   | L    | Н        | Н                  | L    | L    | L    | L    |

Note: 1. Chip Erase requires a 10 ms PROG pulse.

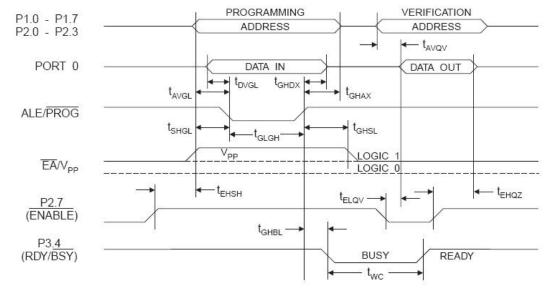

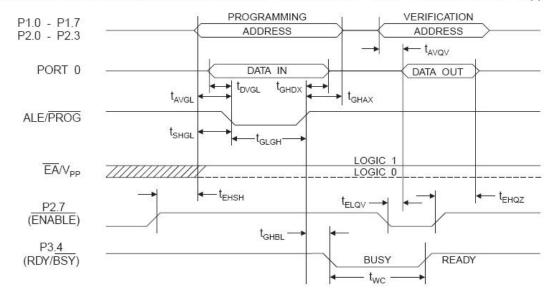

Figure 3. Programming the Flash

Figure 4. Verifying the Flash

# Flash Programming and Verification Waveforms - High-voltage Mode ( $V_{PP} = 12V$ )

# Flash Programming and Verification Waveforms - Low-voltage Mode ( $V_{PP} = 5V$ )

# Flash Programming and Verification Characteristics

$T_A = 0$ °C to 70°C,  $V_{CC} = 5.0 \pm 10$ %

| Symbol                           | Parameter                             | Min                 | Max                 | Units |

|----------------------------------|---------------------------------------|---------------------|---------------------|-------|

| V <sub>PP</sub> <sup>(1)</sup>   | Programming Enable Voltage            | 11.5                | 12.5                | V     |

| I <sub>PP</sub> <sup>(1)</sup>   | Programming Enable Current            |                     | 1.0                 | mA    |

| 1/t <sub>CLCL</sub>              | Oscillator Frequency                  | 3                   | 24                  | MHz   |

| t <sub>AVGL</sub>                | Address Setup to PROG Low             | 48t <sub>CLCL</sub> |                     |       |

| t <sub>GHAX</sub>                | Address Hold after PROG               | 48t <sub>CLCL</sub> |                     |       |

| t <sub>DVGL</sub>                | Data Setup to PROG Low                | 48t <sub>CLCL</sub> |                     |       |

| t <sub>GHDX</sub>                | Data Hold after PROG                  | 48t <sub>CLCL</sub> |                     |       |

| t <sub>EHSH</sub>                | P2.7 (ENABLE) High to V <sub>PP</sub> | 48t <sub>CLCL</sub> |                     |       |

| t <sub>shgL</sub>                | V <sub>PP</sub> Setup to PROG Low     | 10                  |                     | μs    |

| t <sub>GHSL</sub> <sup>(1)</sup> | V <sub>PP</sub> Hold after PROG       | 10                  |                     | μs    |

| t <sub>GLGH</sub>                | PROG Width                            | 1                   | 110                 | μs    |

| t <sub>AVQV</sub>                | Address to Data Valid                 |                     | 48t <sub>cLCL</sub> |       |

| t <sub>ELQV</sub>                | ENABLE Low to Data Valid              |                     | 48t <sub>cLCL</sub> |       |

| t <sub>EHQZ</sub>                | Data Float after ENABLE               | 0                   | 48t <sub>CLCL</sub> |       |

| t <sub>GHBL</sub>                | PROG High to BUSY Low                 |                     | 1.0                 | μs    |

| t <sub>wc</sub>                  | Byte Write Cycle Time                 |                     | 2.0                 | ms    |

Note: 1. Only used in 12-volt programming mode.

# Absolute Maximum Ratings\*

| Operating Temperature     | 55°C to +125°C |

|---------------------------|----------------|

| Storage Temperature       | 65°C to +150°C |

| Voltage on Any Pin        |                |

| with Respect to Ground    | 1.0V to +7.0V  |

| Maximum Operating Voltage | 6.6V           |

| DC Output Current         | 15.0 mA        |

\*NOTICE:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **DC** Characteristics

$T_A = -40$ °C to 85°C,  $V_{CC} = 5.0V \pm 20\%$  (unless otherwise noted)

| Symbol           | Parameter                                                | Condition                                           | Min                       | Max                       | Units |

|------------------|----------------------------------------------------------|-----------------------------------------------------|---------------------------|---------------------------|-------|

| V <sub>IL</sub>  | Input Low-voltage                                        | (Except EA)                                         | -0.5                      | 0.2 V <sub>cc</sub> - 0.1 | ٧     |

| V <sub>IL1</sub> | Input Low-voltage (EA)                                   |                                                     | -0.5                      | 0.2 V <sub>CC</sub> - 0.3 | ٧     |

| V <sub>IH</sub>  | Input High-voltage                                       | (Except XTAL1, RST)                                 | 0.2 V <sub>cc</sub> + 0.9 | V <sub>cc</sub> + 0.5     | ٧     |

| V <sub>IH1</sub> | Input High-voltage                                       | (XTAL1, RST)                                        | 0.7 V <sub>CC</sub>       | V <sub>cc</sub> + 0.5     | ٧     |

| V <sub>OL</sub>  | Output Low-voltage <sup>(1)</sup> (Ports 1,2,3)          | I <sub>OL</sub> = 1.6 mA                            |                           | 0.45                      | ٧     |

| V <sub>OL1</sub> | Output Low-voltage <sup>(1)</sup><br>(Port 0, ALE, PSEN) | I <sub>OL</sub> = 3.2 mA                            |                           | 0.45                      | ٧     |

|                  |                                                          | I <sub>OH</sub> = -60 μA, V <sub>CC</sub> = 5V ±10% | 2.4                       | 9                         | ٧     |

| V <sub>OH</sub>  | Output High-voltage<br>(Ports 1,2,3, ALE, PSEN)          | I <sub>OH</sub> = -25 μA                            | 0.75 V <sub>CC</sub>      |                           | ٧     |

|                  |                                                          | I <sub>OH</sub> = -10 μA                            | 0.9 V <sub>CC</sub>       |                           | ٧     |

|                  | Output High-voltage<br>(Port 0 in External Bus Mode)     | $I_{OH}$ = -800 $\mu$ A, $V_{CC}$ = 5V ±10%         | 2.4                       | da se                     | ٧     |

| V <sub>OH1</sub> |                                                          | I <sub>OH</sub> = -300 μA                           | 0.75 V <sub>cc</sub>      | 51                        | ٧     |

|                  |                                                          | I <sub>OH</sub> = -80 μA                            | 0.9 V <sub>CC</sub>       |                           | ٧     |

| I <sub>IL</sub>  | Logical 0 Input Current (Ports 1,2,3)                    | V <sub>IN</sub> = 0.45V                             |                           | -50                       | μΑ    |

| I <sub>TL</sub>  | Logical 1 to 0 Transition Current<br>(Ports 1,2,3)       | V <sub>IN</sub> = 2V, VCC = 5V ± 10%                |                           | -650                      | μΑ    |

| ILI              | Input Leakage Current (Port 0, EA)                       | 0.45 < V <sub>IN</sub> < V <sub>CC</sub>            |                           | ±10                       | μА    |

| RRST             | Reset Pull-down Resistor                                 |                                                     | 50                        | 300                       | ΚΩ    |

| C <sub>IO</sub>  | Pin Capacitance                                          | Test Freq. = 1 MHz, T <sub>A</sub> = 25°C           |                           | 10                        | pF    |

|                  | B 0                                                      | Active Mode, 12 MHz                                 |                           | 20                        | mΑ    |

| Ē                | Power Supply Current                                     | Idle Mode, 12 MHz                                   | 3                         | 5                         | mA    |

| Icc              | D 4 (2)                                                  | V <sub>CC</sub> = 6V                                |                           | 100                       | μА    |

|                  | Power-down Mode <sup>(2)</sup>                           | V <sub>CC</sub> = 3V                                |                           | 40                        | μА    |

Notes: 1. Under steady state (non-transient) conditions,  $I_{OL}$  must be externally limited as follows:

Maximum I<sub>OL</sub> per port pin: 10 mA

Maximum I<sub>OL</sub> per 8-bit port: Port 0: 26 mA Ports 1, 2, 3: 15 mA

Maximum total  $I_{OL}$  for all output pins: 71 mA

If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

2. Minimum  $V_{CC}$  for Power-down is 2V.

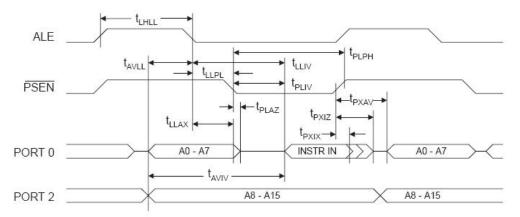

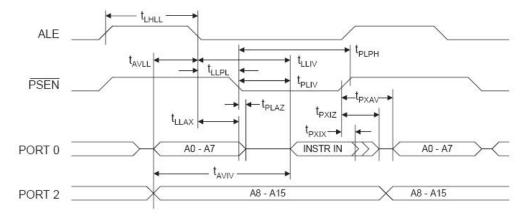

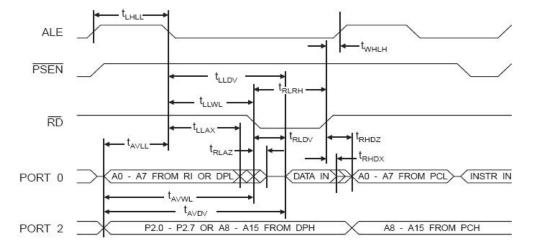

# **External Program Memory Read Cycle**

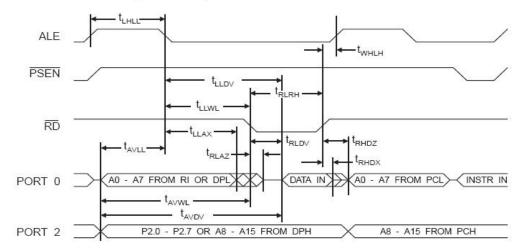

# **External Data Memory Read Cycle**

# **External Program Memory Read Cycle**

# **External Data Memory Read Cycle**

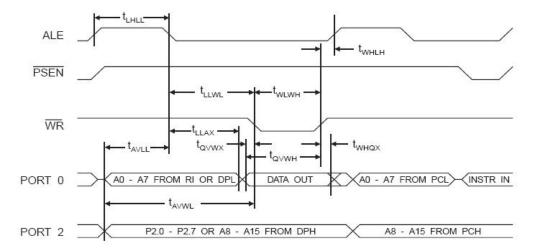

# **External Data Memory Write Cycle**

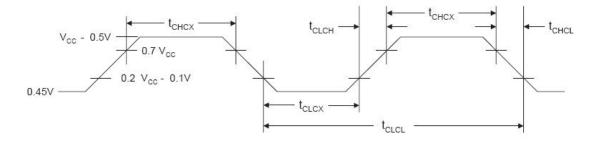

# **External Clock Drive Waveforms**

# **External Clock Drive**

| Symbol              | Parameter            | Min  | Max | Units |

|---------------------|----------------------|------|-----|-------|

| 1/t <sub>CLCL</sub> | Oscillator Frequency | 0    | 24  | MHz   |

| t <sub>CLCL</sub>   | Clock Period         | 41.6 | è   | ns    |

| t <sub>CHCX</sub>   | High Time            | 15   | 6   | ns    |

| t <sub>cLCX</sub>   | Low Time             | 15   |     | ns    |

| t <sub>CLCH</sub>   | Rise Time            | 8    | 20  | ns    |

| t <sub>CHCL</sub>   | Fall Time            |      | 20  | ns    |

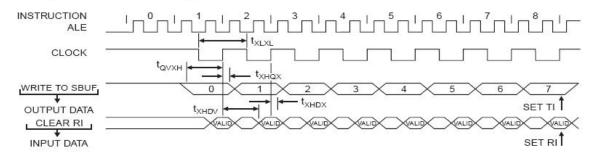

# Serial Port Timing: Shift Register Mode Test Conditions

(V<sub>CC</sub> = 5.0 V ±20%; Load Capacitance = 80 pF)

|                   |                                          | 12 MHz Osc |     | Variable Oscillator      |                          | Units |  |

|-------------------|------------------------------------------|------------|-----|--------------------------|--------------------------|-------|--|

| Symbol            | Parameter                                | Min        | Max | Min                      | Max                      | 1     |  |

| t <sub>XLXL</sub> | Serial Port Clock Cycle Time             | 1.0        |     | 12t <sub>CLCL</sub>      |                          | μs    |  |

| t <sub>QVXH</sub> | Output Data Setup to Clock Rising Edge   | 700        |     | 10t <sub>CLCL</sub> -133 |                          | ns    |  |

| t <sub>xHQX</sub> | Output Data Hold after Clock Rising Edge | 50         |     | 2t <sub>CLCL</sub> -117  |                          | ns    |  |

| t <sub>xHDX</sub> | Input Data Hold after Clock Rising Edge  | 0          |     | 0                        |                          | ns    |  |

| t <sub>XHDV</sub> | Clock Rising Edge to Input Data Valid    |            | 700 |                          | 10t <sub>CLCL</sub> -133 | ns    |  |

# Shift Register Mode Timing Waveforms

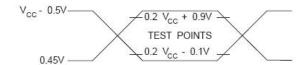

# AC Testing Input/Output Waveforms(1)

# Float Waveforms(1)

AC Inputs during testing are driven at V<sub>CC</sub> - 0.5V for a logic 1 and 0.45V for a logic 0. Timing measurements are made at V<sub>IH</sub> min. for a logic 1 and V<sub>IL</sub> max. for a logic 0. Note: 1. For timing purposes, a port pin is no longer floating when a 100 mV change from load voltage occurs. A port pin begins to float when 100 mV change from the loaded V<sub>OH</sub>/V<sub>OL</sub> level occurs.

# Ordering Information

| Speed<br>(MHz) | Power<br>Supply | Ordering Code | Package | Operation Range   |

|----------------|-----------------|---------------|---------|-------------------|

| 12             | 5V ±20%         | AT89C51-12AC  | 44A     | Commercial        |

|                |                 | AT89C51-12JC  | 44J     | (0°C to 70°C)     |

|                |                 | AT89C51-12PC  | 40P6    |                   |

|                |                 | AT89C51-12QC  | 44Q     |                   |

|                |                 | AT89C51-12AI  | 44A     | Industrial        |

|                |                 | AT89C51-12JI  | 44J     | (-40° C to 85° C) |

|                |                 | AT89C51-12PI  | 40P6    |                   |

|                |                 | AT89C51-12QI  | 44Q     |                   |

| 16             | 5V ±20%         | AT89C51-16AC  | 44A     | Commercial        |

|                |                 | AT89C51-16JC  | 44J     | (0°C to 70°C)     |

|                |                 | AT89C51-16PC  | 40P6    |                   |

|                |                 | AT89C51-16QC  | 44Q     |                   |

|                |                 | AT89C51-16AI  | 44A     | Industrial        |

|                |                 | AT89C51-16JI  | 44J     | (-40° C to 85° C) |

|                |                 | AT89C51-16PI  | 40P6    |                   |

|                |                 | AT89C51-16QI  | 44Q     |                   |

| 20             | 5V ± 20%        | AT89C51-20AC  | 44A     | Commercial        |

|                |                 | AT89C51-20JC  | 44J     | (0° C to 70° C)   |

|                |                 | AT89C51-20PC  | 40P6    |                   |

|                |                 | AT89C51-20QC  | 44Q     |                   |

|                |                 | AT89C51-20AI  | 44A     | Industrial        |

|                |                 | AT89C51-20JI  | 44J     | (-40° C to 85° C) |

|                |                 | AT89C51-20PI  | 40P6    |                   |

|                |                 | AT89C51-20QI  | 44Q     |                   |

| 24             | 5V ± 20%        | AT89C51-24AC  | 44A     | Commercial        |

|                |                 | AT89C51-24JC  | 44J     | (0° C to 70° C)   |

|                |                 | AT89C51-24PC  | 40P6    |                   |

|                |                 | AT89C51-24QC  | 44Q     |                   |

|                |                 | AT89C51-24AI  | 44A     | Industrial        |

|                |                 | AT89C51-24JI  | 44J     | (-40° C to 85° C) |

|                |                 | AT89C51-24PI  | 40P6    |                   |

|                |                 | AT89C51-24QI  | 44Q     |                   |

|                                                          | Package Type                                             |  |  |  |  |  |

|----------------------------------------------------------|----------------------------------------------------------|--|--|--|--|--|

| 44A 44-lead, Thin Plastic Gull Wing Quad Flatpack (TQFP) |                                                          |  |  |  |  |  |

| 44J                                                      | 44-lead, Plastic J-leaded Chip Carrier (PLCC)            |  |  |  |  |  |

| 40P6                                                     | 40-lead, 0.600" Wide, Plastic Dual Inline Package (PDIP) |  |  |  |  |  |

| 44Q                                                      | 44-lead, Plastic Gull Wing Quad Flatpack (PQFP)          |  |  |  |  |  |

# **Packaging Information**

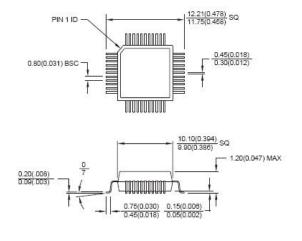

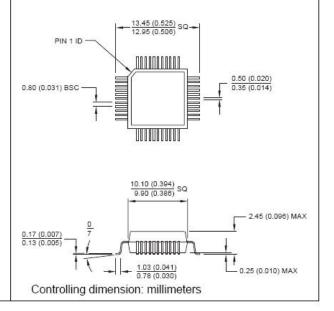

44A, 44-lead, Thin (1.0 mm) Plastic Gull Wing Quad Flatpack (TQFP)

Dimensions in Millimeters and (Inches)\* JEDEC STANDARD MS-026 ACB

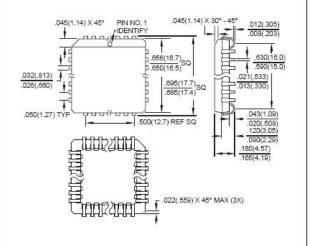

44J, 44-lead, Plastic J-leaded Chip Carrier (PLCC) Dimensions in Inches and (Millimeters) JEDEC STANDARD MS-018 AC

Controlling dimension: millimeters

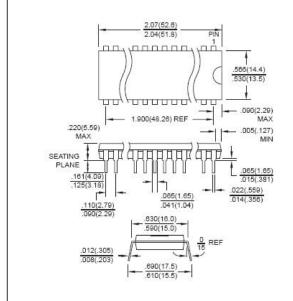

40P6, 40-lead, 0.600" Wide, Plastic Dual Inline Package (PDIP)

Dimensions in Inches and (Millimeters)

44Q, 44-lead, Plastic Quad Flat Package (PQFP) Dimensions in Millimeters and (Inches)\*

JEDEC STANDARD MS-022 AB

# Atmel Headquarters

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL (408) 441-0311 FAX (408) 487-2600

Europe

Atmel U.K., Ltd.

Coliseum Business Centre

Riverside Way

Camberley, Surrey GU15 3YL

England

TEL (44) 1276-686-677

FAX (44) 1276-686-697

Asia

Atmel Asia, Ltd. Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

Japan

Atmel Japan K.K. 9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

# **Atmel Operations**

Atmel Colorado Springs 1150 E. Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL (719) 576-3300 FAX (719) 540-1759

Atmel Rousset

Zone Industrielle

13106 Rousset Cedex

France

TEL (33) 4-4253-6000

FAX (33) 4-4253-6001

Fax-on-Demand North America: 1-(800) 292-8635 International: 1-(408) 441-0732

e-mail literature@atmel.com

Web Site http://www.atmel.com

BBS 1-(408) 436-4309

© Atmel Corporation 2000.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

Marks bearing ® and/or ™ are registered trademarks and trademarks of Atmel Corporation.

Terms and product names in this document may be trademarks of others.

Printed on recycled paper. 0265G-02/00/xM

# LAMPIRAN E DATA KOMPONEN PARALLEL PORT

# Interfacing the Standard Parallel Port

Disclaimer: While every effort has been made to make sure the information in this document is correct, the author can not be liable for any damages whatsoever for loss relating to this document. Use this information at your own risk.

### Table of Contents

| Introduction to Parallel Ports                              | Page 1  |

|-------------------------------------------------------------|---------|

| Hardware Properties                                         | Page 2  |

| Centronics?                                                 | Page 4  |

| Port Addresses                                              | Page 4  |

| Software Registers - Standard Parallel Port (SPP)           | Page 6  |

| Bi-directional Ports                                        | Page 8  |

| Using The Parallel Port to Input 8 Bits.                    | Page 9  |

| Nibble Mode                                                 | Page 11 |

| Using the Parallel Port's IRQ                               | Page 12 |

| Parallel Port Modes in BIOS                                 | Page 14 |

| Parallel Port Modes and the ECP's Extended Control Register | Page 15 |

# Introduction to Parallel Ports

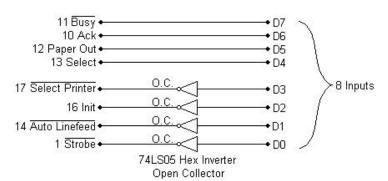

The Parallel Port is the most commonly used port for interfacing home made projects. This port will allow the input of up to 9 bits or the output of 12 bits at any one given time, thus requiring minimal external circuitry to implement many simpler tasks. The port is composed of 4 control lines, 5 status lines and 8 data lines. It's found commonly on the back of your PC as a D-Type 25 Pin female connector. There may also be a D-Type 25 pin male connector. This will be a serial RS-232 port and thus, is a totally incompatible port.

Newer Parallel Port's are standardized under the IEEE 1284 standard first released in 1994. This standard defines 5 modes of operation which are as follows,

- 1. Compatibility Mode.

- 2. Nibble Mode. (Protocol not Described in this Document)

- 3. Byte Mode. (Protocol not Described in this Document)

- 4. EPP Mode (Enhanced Parallel Port).

- 5. ECP Mode (Extended Capabilities Port).

The aim was to design new drivers and devices which were compatible with each other and

Interfacing the Standard Parallel Port

also backwards compatible with the Standard Parallel Port (SPP). Compatibility, Nibble & Byte modes use just the standard hardware available on the original Parallel Port cards while EPP & ECP modes require additional hardware which can run at faster speeds, while still being downwards compatible with the Standard Parallel Port.

Compatibility mode or "Centronics Mode" as it is commonly known, can only send data in the forward direction at a typical speed of 50 kbytes per second but can be as high as 150+ kbytes a second. In order to receive data, you must change the mode to either Nibble or Byte mode. Nibble mode can input a nibble (4 bits) in the reverse direction. E.g. from device to computer. Byte mode uses the Parallel's bi-directional feature (found only on some cards) to input a byte (8 bits) of data in the reverse direction.

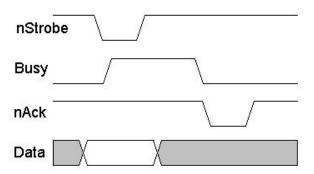

Extended and Enhanced Parallel Ports use additional hardware to generate and manage handshaking. To output a byte to a printer (or anything in that matter) using compatibility mode, the software must.

- 1. Write the byte to the Data Port.

- Check to see is the printer is busy. If the printer is busy, it will not accept any data, thus any data which is written will be lost.

- Take the Strobe (Pin 1) low. This tells the printer that there is the correct data on the data lines. (Pins 2-9)

- Put the strobe high again after waiting approximately 5 microseconds after putting the strobe low. (Step 3)

This limits the speed at which the port can run at. The EPP & ECP ports get around this by letting the hardware check to see if the printer is busy and generate a strobe and /or appropriate handshaking. This means only one I/O instruction need to be performed, thus increasing the speed. These ports can output at around 1-2 megabytes per second. The ECP port also has the advantage of using DMA channels and FIFO buffers, thus data can be shifted around without using I/O instructions.

# Hardware Properties

On the next page is a table of the "Pin Outs" of the D-Type 25 Pin connector and the Centronics 34 Pin connector. The D-Type 25 pin connector is the most common connector found on the Parallel Port of the computer, while the Centronics Connector is commonly found on printers. The IEEE 1284 standard however specifies 3 different connectors for use with the Parallel Port. The first one, 1284 Type A is the D-Type 25 connector found on the back of most computers. The 2nd is the 1284 Type B which is the 36 pin Centronics Connector found on most printers.

IEEE 1284 Type C however, is a 36 conductor connector like the Centronics, but smaller. This connector is claimed to have a better clip latch, better electrical properties and is easier to assemble. It also contains two more pins for signals which can be used to see whether the other device connected,

has power. 1284 Type C connectors are recommended for new designs, so we can look forward on seeing these new connectors in the near future.

| Pin No (D-<br>Type 25) | Pin No<br>(Centronics) | SPP Signal                    | Direction<br>In/out | Register | Hardware<br>Inverted |

|------------------------|------------------------|-------------------------------|---------------------|----------|----------------------|

| 1                      | 1                      | nStrobe                       | In/Out              | Control  | Yes                  |

| 2                      | 2                      | Data 0                        | Out                 | Data     | 3-371-3-2-3          |

| 3                      | 3                      | Data 1                        | Out                 | Data     |                      |

| 4                      | 4                      | Data 2                        | Out                 | Data     |                      |

| 5                      | 5                      | Data 3                        | Out                 | Data     |                      |

| 6                      | 6                      | Data 4                        | Out                 | Data     |                      |

| 7                      | 7                      | Data 5                        | Out                 | Data     |                      |

| 8                      | 8                      | Data 6                        | Out                 | Data     |                      |

| 9                      | 9                      | Data 7                        | Out                 | Data     |                      |

| 10                     | 10                     | nAck                          | In                  | Status   |                      |

| 11                     | 11                     | Busy                          | In                  | Status   | Yes                  |

| 12                     | 12                     | Paper-Out<br>PaperEnd         | In                  | Status   |                      |

| 13                     | 13                     | Select                        | In                  | Status   |                      |

| 14                     | 14                     | nAuto-Linefeed                | In/Out              | Control  | Yes                  |

| 15                     | 32                     | nError / nFault               | In                  | Status   |                      |

| 16                     | 31                     | nInitialize                   | In/Out              | Control  | î                    |

| 17                     | 36                     | nSelect-Printer<br>nSelect-In | In/Out              | Control  | Yes                  |