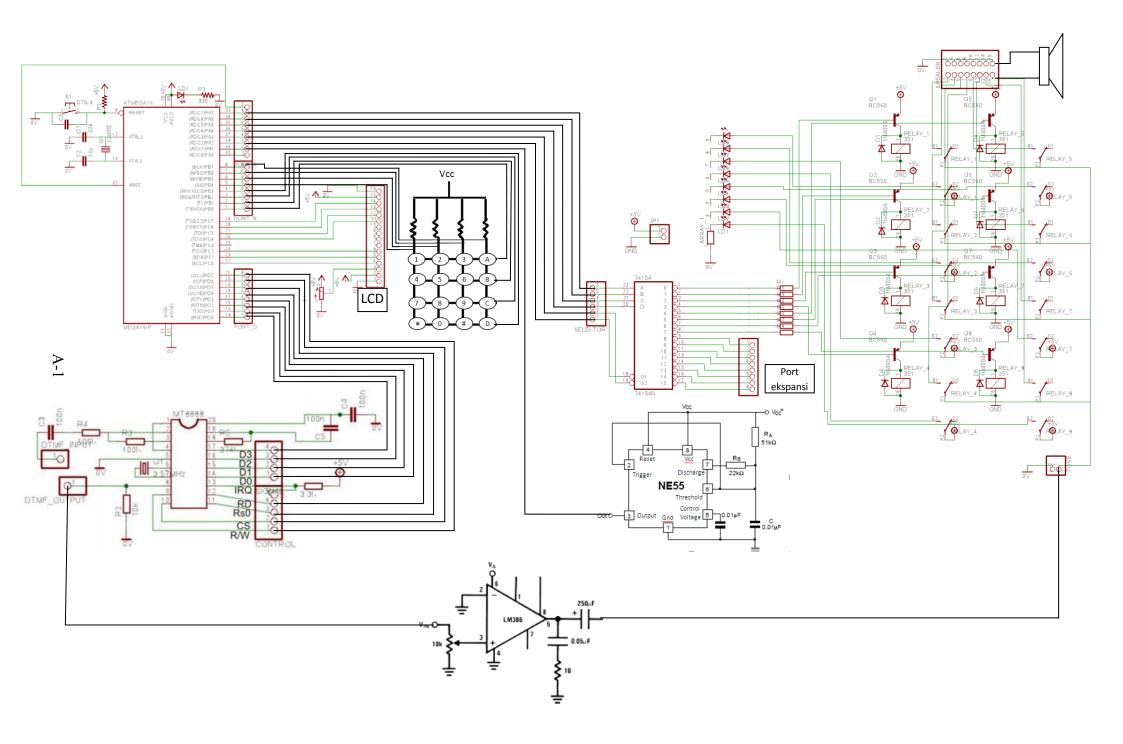

## LAMPIRAN A

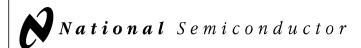

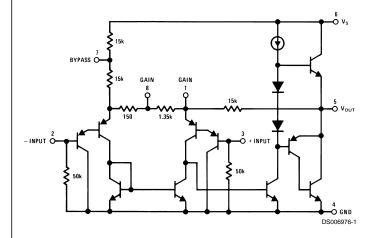

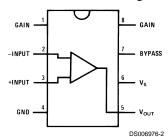

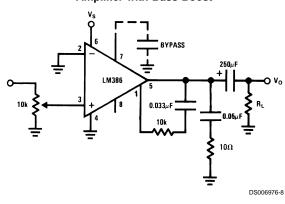

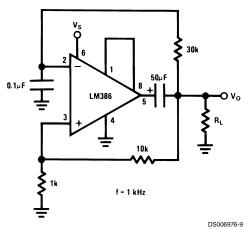

**RANGKAIAN**

# LAMPIRAN B PROGRAM

```

/****************

This program was produced by the

CodeWizardAVR V1.25.3 Professional

Automatic Program Generator

© Copyright 1998-2007 Pavel Haiduc, HP InfoTech s.r.l.

http://www.hpinfotech.com

Project:

Version:

Date : 11/25/2009

Author: Edwin

Company: Bonzo

Comments:

Chip type

: ATmega16

: Application

Program type

Clock frequency : 16.000000 MHz

Memory model

: Small

External SRAM size : 0

Data Stack size : 256

#include <mega16.h>

#include <delay.h>

#include <stdio.h>

// Alphanumeric LCD Module functions

#asm

.equ __lcd_port=0x15 ;PORTC

#endasm

#include <lcd.h>

int del;

#define PORT PORTD

#define d3 PORT.0

#define d2 PORT.1

#define d1 PORT.2

#define d0 PORT.3

#define wr PORT.7

#define cs PORT.6

#define rs0 PORT.5

#define rd PORT.4

#define delay delay ms(del)

#define telkomsel 0x00

#define indosat 0x04

#define xl 0x08

#define axis 0x0C

#define three 0x10

```

#define cdma\_roaming 0x14

```

#define cdma lokal 0x18

#define tlp_rmh 0x1C

// Declare your global variables here

char text[30];

char keypressed;

char no_tlp[12];

int i,j,k;

int dial[12],cal_tone,hitung;

void no_line(void)

{lcd_clear();

lcd_putsf("Maaf, Saluran");

lcd gotoxy(0,1);

lcd_putsf("tidak terhubung");

delay_ms(3000);

i=0; no_tlp[0]=' ';no_tlp[1]=' ';no_tlp[2]=' ';no_tlp[3]=' ';no_tlp[4]=' ';no_tlp[5]='

';no_tlp[6]=' ';no_tlp[7]=' ';no_tlp[8]=' ';no_tlp[9]=' ';no_tlp[10]=' ';no_tlp[11]=' ';

dial[0]=0;dial[1]=0;dial[2]=0;dial[3]=0;dial[4]=0;dial[5]=0;dial[6]=0;dial[7]=0;dial[8]=0;dial[8]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9]=0;dial[9

I[9]=0;dial[10]=0;dial[11]=0;k=0;

void out (char output)

DDRD=255;

wr=1;rd=1;rs0=1;cs=0;

if(output==1)

{d0=1;d1=0;d2=0;d3=1;}

else

{d0=0;d1=0;d2=0;d3=1;}

wr=0;

delay_us(1);

wr=1;

delay_us(1);

if(output==1)

{d0=1;d1=0;d2=0;d3=0;}

else

{d0=0;d1=0;d2=0;d3=0;}

wr=0;

delay_us(1);

wr=1;

delay_us(1);

}

```

```

void dtmf (char input)

DDRD=0xFF;

rd=1;

wr=1;

cs=0;

rs0=0;

delay_us(1);

switch(input)

case 1: d3=0;d2=0;d1=0;d0=1;break;

case 2: d3=0;d2=0;d1=1;d0=0;break;

case 3: d3=0;d2=0;d1=1;d0=1;break;

case 4: d3=0;d2=1;d1=0;d0=0;break;

case 5: d3=0;d2=1;d1=0;d0=1;break;

case 6: d3=0;d2=1;d1=1;d0=0;break;

case 7: d3=0;d2=1;d1=1;d0=1;break;

case 8: d3=1;d2=0;d1=0;d0=0;break;

case 9: d3=1;d2=0;d1=0;d0=1;break;

case 0: d3=1;d2=0;d1=1;d0=0;break;

case '*':d3=1;d2=0;d1=1;d0=1;break;

case '#':d3=1;d2=1;d1=0;d0=0;break;

case 'a':d3=1;d2=1;d1=0;d0=1;break;

case 'b':d3=1;d2=1;d1=1;d0=0;break;

case 'c':d3=1;d2=1;d1=1;d0=1;break;

case 'd':d3=0;d2=0;d1=0;d0=0;break;

}

wr=0;

delay_us(1);

wr=1;

delay_us(1);

}

void tone (void)

{

cal_tone=0;

hitung=0;

DDRA.1=0;

PORTA.1=1;

periksa1:

if (PINA.1==0)

goto periksa2;

goto periksa1;

periksa2:

if (PINA.1==1)

```

```

{hitung=0;

goto periksa3;}

else

{hitung=hitung+1;

delay_us(1);

if (hitung<2000)

{goto periksa2;}

else

{no_line();}

periksa3:

if (PINA.1==0)

goto periksa4;

cal_tone=cal_tone+1;

goto periksa3;

periksa4:

if (cal_tone<1500 && cal_tone>1000)

{goto tone_panggil;}

else

{no_line();}

tone panggil:

del=200;

for (j=0;j<i;j++)

out(1);dtmf(dial[j]);delay;out(0);delay;

}

PORTA=0xFC;

delay_ms(5);

i=0; no_tlp[0]=' ';no_tlp[1]=' ';no_tlp[2]=' ';no_tlp[3]=' ';no_tlp[4]=' ';no_tlp[5]='

';no_tlp[6]=' ';no_tlp[7]=' ';no_tlp[8]=' ';no_tlp[9]=' ';no_tlp[10]=' ';no_tlp[11]=' ';

\label{eq:dial_0} \\ \text{dial}[0]=0;\\ \text{dial}[1]=0;\\ \text{dial}[2]=0;\\ \text{dial}[3]=0;\\ \text{dial}[4]=0;\\ \text{dial}[5]=0;\\ \text{dial}[6]=0;\\ \text{dial}[7]=0;\\ \text{dial}[8]=0;\\ \text{dial}[8]=0;\\

I[9]=0;dial[10]=0;dial[11]=0;k=0;

}

void selektor (void)

if (i>=10 && i<=12 && no_tlp[0]=='0' && no_tlp[1]=='8')

if (no_tlp[2]=='1')

if (no_tlp[3]=='7'|| no_tlp[3]=='8'||no_tlp[3]=='9')

lcd_gotoxy(0,1);

lcd_putsf("XL");

PORTA=xI;

delay_ms(5);

tone(); }

```

```

if (no_tlp[3]=='5'||no_tlp[3]=='6')

lcd_gotoxy(0,1);

lcd_putsf("Mentari");

PORTA=indosat;

delay_ms(5);

tone();

}

if (no_tlp[3]=='1'||no_tlp[3]=='2'||no_tlp[3]=='3')

lcd gotoxy(0,1);

lcd_putsf("Telkomsel");

PORTA=telkomsel;

delay_ms(5);

tone();

}

}

if (no_tlp[2]=='3')

if (no_tlp[3]=='8')

lcd_gotoxy(0,1);

lcd_putsf("Axis");

PORTA=axis;

delay_ms(5);

tone();

}

}

if (no_tlp[2]=='5')

if (no_tlp[3]=='5'||no_tlp[3]=='6'||no_tlp[3]=='7'||no_tlp[3]=='8')

lcd_gotoxy(0,1);

lcd putsf("Indosat");

PORTA=indosat;

delay_ms(5);

tone();

if (no_tlp[3]=='2'||no_tlp[3]=='3')

lcd_gotoxy(0,1);

lcd putsf("AS");

PORTA=telkomsel;

delay_ms(5);

tone();

}

}

if (no_tlp[2]=='7')

if (no_tlp[3]=='7'| |no_tlp[3]=='8')

```

```

lcd_gotoxy(0,1);

lcd_putsf("XL");

PORTA=xl;

delay_ms(5);

tone();

}

if (no_tlp[2]=='8')

if (no_tlp[3]=='8'||no_tlp[3]=='9')

lcd_gotoxy(0,1);

lcd_putsf("Fren");

PORTA=cdma_roaming;

delay_ms(5);

tone();

}

if (no_tlp[3]=='2')

lcd_gotoxy(0,1);

lcd_putsf("Smart");

PORTA=cdma_roaming;

delay_ms(5);

tone();

}

}

if (no_tlp[2]=='9')

if (no_tlp[3]=='6'||no_tlp[3]=='8')

{

lcd_gotoxy(0,1);

lcd_putsf("Three");

PORTA=three;

delay_ms(5);

tone();

}

}

}

if (i==8)

if (no_tlp[0]=='2')

lcd_gotoxy(0,1);

lcd_putsf("Hepi");

PORTA=cdma_lokal;

delay_ms(5);

tone();

if (no_tlp[0]=='3')

```

```

lcd_gotoxy(0,1);

lcd_putsf("Star One");

PORTA=cdma_lokal;

delay_ms(5);

tone();

if (no_tlp[0]=='7')

lcd_gotoxy(0,1);

lcd putsf("Flexi");

PORTA=cdma_lokal;

delay_ms(5);

tone();

if (no_tlp[0]=='9')

lcd_gotoxy(0,1);

lcd_putsf("Esia");

PORTA=cdma lokal;

delay_ms(5);

tone();

}

}

if (i==7)

{lcd_gotoxy(0,1);

lcd_putsf("Tlp Rumah");

PORTA=tlp rmh;

delay_ms(5);

tone();

if (i>=3 && i<=12)

{lcd_gotoxy(0,1);

lcd putsf("other");

PORTA=tlp_rmh;

delay_ms(5);

tone();

else

i=0;

no\_tlp[0]=' \ '; no\_tlp[1]=' \ '; no\_tlp[2]=' \ '; no\_tlp[3]=' \ '; no\_tlp[4]=' \ '; no\_tlp[5]=' \ '; no\_tlp[6]=' \ '; no\_t

';no_tlp[7]=' ';no_tlp[8]=' ';no_tlp[9]=' ';no_tlp[10]=' ';no_tlp[11]=' ';

dial[0]=0;dial[1]=0;dial[2]=0;dial[3]=0;dial[4]=0;dial[5]=0;dial[6]=0;dial[7]=0;dial[8]=0;dial

I[9]=0;dial[10]=0;dial[11]=0;

}

}

```

```

char scan_keypadB_rev(void)

int scankey;

unsigned char keypressed=0;

char temp;

temp=PORTB;

DDRB = 0x0F;

PORTB = 0xFE;

delay us(1);

scankey = PINB&0xf0;

k=k+1;

if(k<30)

{

switch (scankey)

case 0xE0 : PORTA=0xD1;delay_ms(1);keypressed = 1;

del=200;out(1);dtmf(1);delay;out(0);delay; no_tlp[i]='1';dial[i]=1;

i++;k=0;PORTA=0xD0;delay_ms(1);break;

case 0xD0 : PORTA=0xD1;delay_ms(1);keypressed = 2;

del=200;out(1);dtmf(2);delay;out(0);delay; no tlp[i]='2';dial[i]=2;

i++;k=0;PORTA=0xD0;delay ms(1);break;

case 0xB0 : PORTA=0xD1;delay_ms(1);keypressed = 3;

del=200;out(1);dtmf(3);delay;out(0);delay; no_tlp[i]='3';dial[i]=3;

i++;k=0;PORTA=0xD0;delay ms(1);break;

case 0x70 : keypressed = 'A'; break;

}

cek1:

scankey = PINB&0xf0; delay us(1);

switch (scankey)

case 0xf0: goto lanjut2;

default: goto cek1;

}

lanjut2:

PORTB = 0xFD;

delay us(1);

scankey = PINB&0xf0;

switch (scankey)

case 0xE0 : PORTA=0xD1;delay ms(1);keypressed = 4;

del=200;out(1);dtmf(4);delay;out(0);delay; no tlp[i]='4';dial[i]=4;

i++;k=0;PORTA=0xD0;delay ms(1);break;

case 0xD0 : PORTA=0xD1;delay_ms(1);keypressed = 5;

del=200;out(1);dtmf(5);delay;out(0);delay; no_tlp[i]='5';dial[i]=5;

i++;k=0;PORTA=0xD0;delay_ms(1);break;

case 0xB0 : PORTA=0xD1;delay ms(1);keypressed = 6;

del=200;out(1);dtmf(6);delay;out(0);delay; no_tlp[i]='6';dial[i]=6;

i++;k=0;PORTA=0xD0;delay_ms(1);break;

case 0x70: keypressed = 'B'; selektor();k=0; break;

```

```

}

cek2:

scankey = PINB&0xf0; delay_us(1);

switch (scankey)

case 0xf0: goto lanjut3;

default: goto cek2;

}

lanjut3:

PORTB = 0xFB;

delay us(1);

scankey = PINB&0xf0;

switch (scankey)

case 0xE0 : PORTA=0xD1;delay_ms(1);keypressed = 7;

del=200;out(1);dtmf(7);delay;out(0);delay; no_tlp[i]='7';dial[i]=7;

i++;k=0;PORTA=0xD0;delay_ms(1);break;

case 0xD0 : PORTA=0xD1;delay_ms(1);keypressed = 8;

del=200;out(1);dtmf(8);delay;out(0);delay; no tlp[i]='8';dial[i]=8;

i++;k=0;PORTA=0xD0;delay_ms(1);break;

case 0xB0 : PORTA=0xD1;delay_ms(1);keypressed = 9;

del=200;out(1);dtmf(9);delay;out(0);delay; no_tlp[i]='9';dial[i]=9;

i++;k=0;PORTA=0xD0;delay ms(1);break;

case 0x70 : keypressed = 'C';

i=0; no_tlp[0]=' ';no_tlp[1]=' ';no_tlp[2]=' ';no_tlp[3]=' ';no_tlp[4]=' ';no_tlp[5]='

';no_tlp[6]=' ';no_tlp[7]=' ';no_tlp[8]=' ';no_tlp[9]=' ';no_tlp[10]=' ';no_tlp[11]=' ';

dial[0]=0; dial[1]=0; dial[2]=0; dial[3]=0; dial[4]=0; dial[5]=0; dial[6]=0; dial[7]=0; dial[8]=0; dial[9]=0; dial[9]=0

I[9]=0;dial[10]=0;dial[11]=0;k=0;

break;

}

cek3:

scankey = PINB&0xf0; delay us(1);

switch (scankey)

case 0xf0: goto lanjut4;

default: goto cek3;

}

lanjut4:

PORTB = 0xF7;

delay us(1);

scankey = PINB&0xf0;

switch (scankey)

{

case 0xE0 : PORTA=0xD1;delay_ms(1);keypressed = '*';

del=200;out(1);dtmf('*');delay;out(0);delay; no_tlp[i]='*';dial[i]='*'; i++;

k=0;PORTA=0xD0;delay_ms(1);break;

```

```

case 0xD0 : PORTA=0xD1;delay ms(1);keypressed = '0';

del=200;out(1);dtmf(0);delay;out(0);delay; no_tlp[i]='0';dial[i]=0; i++;

k=0;PORTA=0xD0;delay_ms(1);break;

case 0xB0 : PORTA=0xD1;delay_ms(1);keypressed = '#';

del=200;out(1);dtmf('#');delay;out(0);delay; no_tlp[i]='#';dial[i]='#'; i++;

k=0;PORTA=0xD0;delay ms(1);break;

case 0x70 : keypressed = 'D'; i=i-1; no_tlp[i]=' ';k=0; break;

}

cek4:

scankey = PINB&0xf0; delay us(1);

switch (scankey)

{

case 0xf0: goto lanjut5;

default: goto cek4;

lanjut5:

return keypressed;

}

else

{k=0;

selektor();

//tone();

}

}

void main(void)

// Declare your local variables here

// Input/Output Ports initialization

// Port A initialization

// Func7=Out Func6=Out Func5=Out Func4=Out Func3=Out Func2=Out Func1=Out

Func0=Out

// State7=0 State6=0 State5=0 State4=0 State3=0 State2=0 State1=0 State0=0

PORTA=0b11000000;

DDRA=0xFF;

// Port B initialization

// Func7=In Func6=In Func5=In Func4=In Func3=In Func2=In Func1=In Func0=In

// State7=T State6=T State5=T State4=T State3=T State2=T State1=T State0=T

PORTB=0x00;

DDRB=0x00;

// Port C initialization

// Func7=In Func6=In Func5=In Func4=In Func3=In Func2=In Func1=In Func0=In

// State7=T State6=T State5=T State4=T State3=T State2=T State1=T State0=T

PORTC=0x00;

DDRC=0x00;

```

```

// Port D initialization

// Func7=In Func6=In Func5=In Func4=In Func3=In Func2=In Func1=In Func0=In

// State7=T State6=T State5=T State4=T State3=T State2=T State1=T State0=T

PORTD=0x00;

DDRD=0x00;

// Timer/Counter 0 initialization

// Clock source: System Clock

// Clock value: Timer 0 Stopped

// Mode: Normal top=FFh

// OC0 output: Disconnected

TCCR0=0x00;

TCNT0=0x00;

OCR0=0x00;

// Timer/Counter 1 initialization

// Clock source: System Clock

// Clock value: Timer 1 Stopped

// Mode: Normal top=FFFFh

// OC1A output: Discon.

// OC1B output: Discon.

// Noise Canceler: Off

// Input Capture on Falling Edge

// Timer 1 Overflow Interrupt: Off

// Input Capture Interrupt: Off

// Compare A Match Interrupt: Off

// Compare B Match Interrupt: Off

TCCR1A=0x00;

TCCR1B=0x00;

TCNT1H=0x00;

TCNT1L=0x00;

ICR1H=0x00;

ICR1L=0x00;

OCR1AH=0x00;

OCR1AL=0x00;

OCR1BH=0x00;

OCR1BL=0x00;

// Timer/Counter 2 initialization

// Clock source: System Clock

// Clock value: Timer 2 Stopped

// Mode: Normal top=FFh

// OC2 output: Disconnected

ASSR=0x00;

TCCR2=0x00;

TCNT2=0x00;

OCR2=0x00;

// External Interrupt(s) initialization

// INTO: Off

```

```

// INT1: Off

// INT2: Off

MCUCR=0x00;

MCUCSR=0x00;

// Timer(s)/Counter(s) Interrupt(s) initialization

TIMSK=0x00;

// Analog Comparator initialization

// Analog Comparator: Off

// Analog Comparator Input Capture by Timer/Counter 1: Off

ACSR=0x80;

SFIOR=0x00;

// LCD module initialization

lcd_init(16);

k=0;

while (1)

// Place your code here

if (i<1)

{lcd_clear();

lcd_putsf("Masukan Nomor yg");

lcd_gotoxy(0,1);

lcd_putsf("Dituju");

delay_ms(250);

}

else

lcd_clear();

sprintf(text,"%c%c%c%c%c%c%c%c%c%c%c%c",no_tlp[0],no_tlp[1],no_tlp[2],no_tlp[3],

no_tlp[4],no_tlp[5],no_tlp[6],no_tlp[7],no_tlp[8],no_tlp[9],no_tlp[10],no_tlp[11]);

lcd_puts(text);

delay_ms(100);

}

scan_keypadB_rev();

};

}

```

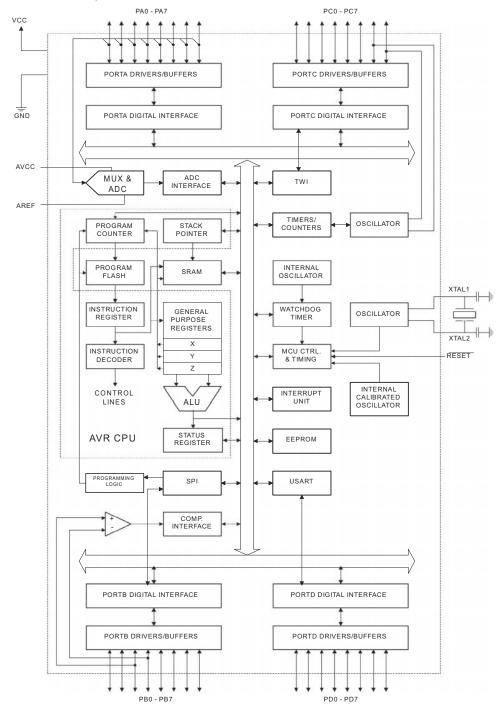

# LAMPIRAN C DATASHEET ATMEGA 16

#### **Features**

- High-performance, Low-power AVR® 8-bit Microcontroller

- · Advanced RISC Architecture

- 131 Powerful Instructions Most Single-clock Cycle Execution

- 32 x 8 General Purpose Working Registers

- Fully Static Operation

- Up to 16 MIPS Throughput at 16 MHz

- On-chip 2-cycle Multiplier

- · High Endurance Non-volatile Memory segments

- 16K Bytes of In-System Self-programmable Flash program memory

- 512 Bytes EEPROM

- 1K Byte Internal SRAM

- Write/Erase Cycles: 10,000 Flash/100,000 EEPROM

- Data retention: 20 years at 85°C/100 years at 25°C<sup>(1)</sup>

- Optional Boot Code Section with Independent Lock Bits In-System Programming by On-chip Boot Program

- True Read-While-Write Operation

- Programming Lock for Software Security

- JTAG (IEEE std. 1149.1 Compliant) Interface

- Boundary-scan Capabilities According to the JTAG Standard

- Extensive On-chip Debug Support

- Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface

- · Peripheral Features

- Two 8-bit Timer/Counters with Separate Prescalers and Compare Modes

- One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture Mode

- Real Time Counter with Separate Oscillator

- Four PWM Channels

- 8-channel, 10-bit ADC

- 8 Single-ended Channels

- 7 Differential Channels in TQFP Package Only

- 2 Differential Channels with Programmable Gain at 1x, 10x, or 200x

- Byte-oriented Two-wire Serial Interface

- Programmable Serial USART

- Master/Slave SPI Serial Interface

- Programmable Watchdog Timer with Separate On-chip Oscillator

- On-chip Analog Comparator

- Special Microcontroller Features

- Power-on Reset and Programmable Brown-out Detection

- Internal Calibrated RC Oscillator

- External and Internal Interrupt Sources

- Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby and Extended Standby

- I/O and Packages

- 32 Programmable I/O Lines

- 40-pin PDIP, 44-lead TQFP, and 44-pad QFN/MLF

- Operating Voltages

- 2.7 5.5V for ATmega16L

- 4.5 5.5V for ATmega16

- Speed Grades

- 0 8 MHz for ATmega16L

- 0 16 MHz for ATmega16

- Power Consumption @ 1 MHz, 3V, and 25°C for ATmega16L

- Active: 1.1 mA

- Idle Mode: 0.35 mA

- Power-down Mode: < 1 μA

8-bit AVR®

Microcontroller

with 16K Bytes

In-System

Programmable

Flash

ATmega16 ATmega16L

Summary

### Pin Configurations

Figure 1. Pinout ATmega16

#### TQFP/QFN/MLF

4443424140393837363534 (MOSI) PB5 PA4 (ADC4) (MISO) PB6 (SCK) PB7 2 32 PA5 (ADC5) 3 31 PA6 (ADC6) RESET 4 30 PA7 (ADC7) VCC 5 29 AREF 6 28 GND GND XTAL2 7 27 AVCC 26 8 XTAL1 PC7 (TOSC2) (RXD) PD0 9 25 PC6 (TOSC1) 10 24 (TXD) PD1 PC5 (TDI) PC4 (TDO) 11 (INT0) PD2 12<sup>13</sup>14<sup>15</sup>16<sup>17</sup>18<sup>19</sup>20<sup>21</sup>22 NOTE: Bottom pad should be soldered to ground.

#### Disclaimer

Typical values contained in this datasheet are based on simulations and characterization of other AVR microcontrollers manufactured on the same process technology. Min and Max values will be available after the device is characterized.

#### 2 ATmega16(L)

2466PS-AVR-08/07

#### Overview

The ATmega16 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega16 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

#### **Block Diagram**

Figure 2. Block Diagram

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATmega16 provides the following features: 16K bytes of In-System Programmable Flash Program memory with Read-While-Write capabilities, 512 bytes EEPROM, 1K byte SRAM, 32 general purpose I/O lines, 32 general purpose working registers, a JTAG interface for Boundaryscan, On-chip Debugging support and programming, three flexible Timer/Counters with compare modes, Internal and External Interrupts, a serial programmable USART, a byte oriented Two-wire Serial Interface, an 8-channel, 10-bit ADC with optional differential input stage with programmable gain (TQFP package only), a programmable Watchdog Timer with Internal Oscillator, an SPI serial port, and six software selectable power saving modes. The Idle mode stops the CPU while allowing the USART, Two-wire interface, A/D Converter, SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next External Interrupt or Hardware Reset. In Power-save mode, the Asynchronous Timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction mode stops the CPU and all I/O modules except Asynchronous Timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the crystal/resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low-power consumption. In Extended Standby mode, both the main Oscillator and the Asynchronous Timer continue to run.

The device is manufactured using Atmel's high density nonvolatile memory technology. The Onchip ISP Flash allows the program memory to be reprogrammed in-system through an SPI serial interface, by a conventional nonvolatile memory programmer, or by an On-chip Boot program running on the AVR core. The boot program can use any interface to download the application program in the Application Flash memory. Software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega16 is a powerful microcontroller that provides a highly-flexible and cost-effective solution to many embedded control applications.

The ATmega16 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits.

#### **Pin Descriptions**

VCC Digital supply voltage.

GND Ground.

Port A (PA7..PA0) Port A serves as the analog inputs to the A/D Converter.

Port A also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used. Port pins can provide internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. When pins PA0 to PA7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.

#### ا ATmega16(L) ا

2466PS-AVR-08/07

#### Port B (PB7..PB0)

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port B also serves the functions of various special features of the ATmega16 as listed on page 58.

#### Port C (PC7..PC0)

Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running. If the JTAG interface is enabled, the pull-up resistors on pins PC5(TDI), PC3(TMS) and PC2(TCK) will be activated even if a reset occurs.

Port C also serves the functions of the JTAG interface and other special features of the ATmega16 as listed on page 61.

#### Port D (PD7..PD0)

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port D also serves the functions of various special features of the ATmega16 as listed on page 63.

#### RESET

Reset Input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. The minimum pulse length is given in Table 15 on page 38. Shorter pulses are not guaranteed to generate a reset.

XTAL1

Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.

XTAL2

Output from the inverting Oscillator amplifier.

AVCC

AVCC is the supply voltage pin for Port A and the A/D Converter. It should be externally connected to  $V_{CC}$ , even if the ADC is not used. If the ADC is used, it should be connected to  $V_{CC}$  through a low-pass filter.

**AREF**

AREF is the analog reference pin for the A/D Converter.

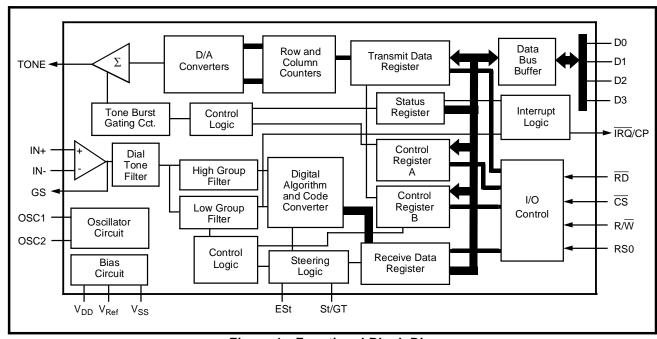

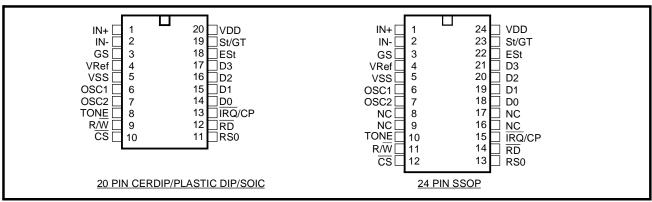

## LAMPIRAN D

**DATASHEET MT8888**

#### MT8888C/MT8888C-1

### Integrated DTMF Transceiver with Intel Micro Interface

**Features**

ISSUE 2 May 1995

- Central office quality DTMF transmitter/receiver

- Low power consumption

- · High speed Intel micro interface

- · Adjustable guard time

- Automatic tone burst mode

- Call progress tone detection to -30dBm

#### **Applications**

- Credit card systems

- · Paging systems

- · Repeater systems/mobile radio

- Interconnect dialers

- Personal computers

#### **Description**

The MT8888C is a monolithic DTMF transceiver with call progress filter. It is fabricated in CMOS technology offering low power consumption and high reliability.

**Ordering Information**

MT8888CE/CE-1 20 Pin Plastic DIP MT8888CC/CC-1 20 Pin Ceramic DIP

MT8888CS/CS-1 20 Pin SOIC MT8888CN/CN-1 24 Pin SSOP

-40°C to +85°C

The receiver section is based upon the industry standard MT8870 DTMF receiver while the transmitter utilizes a switched capacitor D/A converter for low distortion, high accuracy DTMF signalling. Internal counters provide a burst mode such that tone bursts can be transmitted with precise timing. A call progress filter can be selected allowing a microprocessor to analyze call progress tones.

The MT8888C utilizes an Intel micro interface, which allows the device to be connected to a number of popular microcontrollers with minimal external logic. The MT8888C-1 is functionally identical to the MT8888C except the receiver is enhanced to accept lower level signals, and also has a specified low signal rejection level.

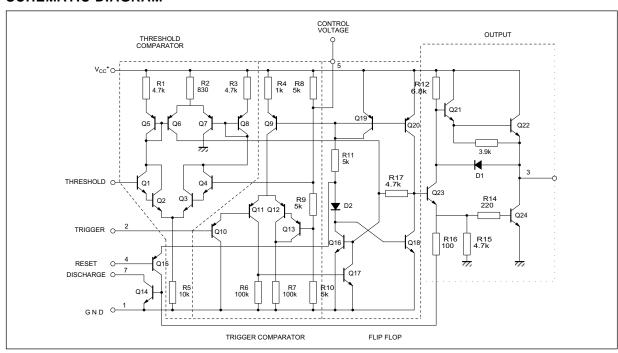

Figure 1 - Functional Block Diagram

D-1 4-91

Figure 2 - Pin Connections

#### **Pin Description**

| Piı       | า #          |            |                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------|--------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20        | 24           | Name       | Description                                                                                                                                                                                                                                                                                                                                                                                  |

| 1         | 1            | IN+        | Non-inverting op-amp input.                                                                                                                                                                                                                                                                                                                                                                  |

| 2         | 2            | IN-        | Inverting op-amp input.                                                                                                                                                                                                                                                                                                                                                                      |

| 3         | 3            | GS         | Gain Select. Gives access to output of front end differential amplifier for connection of feedback resistor.                                                                                                                                                                                                                                                                                 |

| 4         | 4            | $V_{Ref}$  | Reference Voltage output (V <sub>DD</sub> /2).                                                                                                                                                                                                                                                                                                                                               |

| 5         | 5            | $V_{SS}$   | Ground (0V).                                                                                                                                                                                                                                                                                                                                                                                 |

| 6         | 6            | OSC1       | Oscillator input. This pin can also be driven directly by an external clock.                                                                                                                                                                                                                                                                                                                 |

| 7         | 7            | OSC2       | Oscillator output. A 3.579545 MHz crystal connected between OSC1 and OSC2 completes the internal oscillator circuit. Leave open circuit when OSC1 is driven externally.                                                                                                                                                                                                                      |

| 8         | 10           | TONE       | Output from internal DTMF transmitter.                                                                                                                                                                                                                                                                                                                                                       |

| 9         | 11           | WR         | Write microprocessor input. TTL compatible.                                                                                                                                                                                                                                                                                                                                                  |

| 10        | 12           | CS         | Chip Select input. Active Low. This signal must be qualified externally by address latch enable (ALE) signal, see Figure 12.                                                                                                                                                                                                                                                                 |

| 11        | 13           | RS0        | Register Select input. Refer to Table 3 for bit interpretation. TTL compatible.                                                                                                                                                                                                                                                                                                              |

| 12        | 14           | RD         | Read microprocessor input. TTL compatible.                                                                                                                                                                                                                                                                                                                                                   |

| 13        | 15           | ĪRQ/<br>CP | Interrupt Request/Call Progress (open drain) output. In interrupt mode, this output goes low when a valid DTMF tone burst has been transmitted or received. In call progress mode, this pin will output a rectangular signal representative of the input signal applied at the input op-amp. The input signal must be within the bandwidth limits of the call progress filter, see Figure 8. |

| 14-<br>17 | 18-<br>21    | D0-D3      | Microprocessor Data Bus. High impedance when $\overline{CS} = 1$ or $\overline{RD} = 1$ . TTL compatible.                                                                                                                                                                                                                                                                                    |

| 18        | 22           | ESt        | <b>Early Steering</b> output. Presents a logic high once the digital algorithm has detected a valid tone pair (signal condition). Any momentary loss of signal condition will cause ESt to return to a logic low.                                                                                                                                                                            |

| 19        | 23           | St/GT      | <b>Steering Input/Guard Time</b> output (bidirectional). A voltage greater than $V_{TSt}$ detected at St causes the device to register the detected tone pair and update the output latch. A voltage less than $V_{TSt}$ frees the device to accept a new tone pair. The GT output acts to reset the external steering time-constant; its state is a function of ESt and the voltage on St.  |

| 20        | 24           | $V_{DD}$   | Positive power supply (5V typ.).                                                                                                                                                                                                                                                                                                                                                             |

|           | 8,9<br>16,17 | NC         | No Connection.                                                                                                                                                                                                                                                                                                                                                                               |

4-92 D-2

#### **Functional Description**

The MT8888C/MT8888C-1 Integrated DTMF Transceiver consists of a high performance DTMF receiver with an internal gain setting amplifier and a DTMF generator which employs a burst counter to synthesize precise tone bursts and pauses. A call progress mode can be selected so that frequencies within the specified passband can be detected. The Intel micro interface allows microcontrollers, such as the 8080, 80C31/51 and 8085, to access the MT8888C/MT8888C-1 internal registers.

#### **Input Configuration**

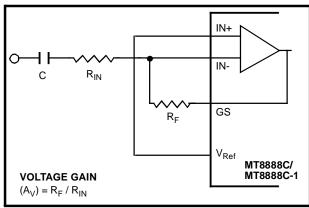

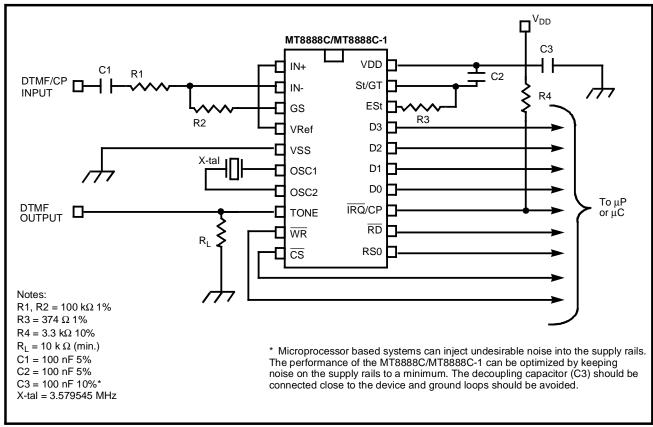

The input arrangement of the MT8888C/MT8888C-1 provides a differential-input operational amplifier as well as a bias source ( $V_{Ref}$ ), which is used to bias the inputs at  $V_{DD}/2$ . Provision is made for connection of a feedback resistor to the op-amp output (GS) for gain adjustment. In a single-ended configuration, the input pins are connected as shown in Figure 3.

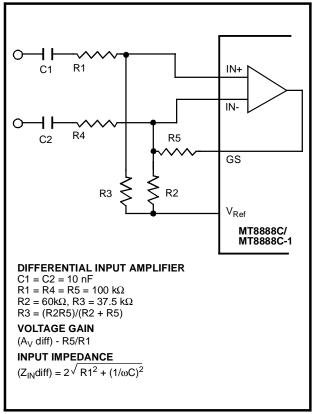

Figure 4 shows the necessary connections for a differential input configuration.

#### **Receiver Section**

Separation of the low and high group tones is achieved by applying the DTMF signal to the inputs of two sixth-order switched capacitor bandpass filters, the bandwidths of which correspond to the low and high group frequencies (see Table 1). These filters incorporate notches at 350 Hz and 440 Hz for exceptional dial tone rejection. Each filter output is followed by a single order switched capacitor filter section, which smooths the signals prior to limiting. Limiting is performed by high-gain comparators which are provided with hysteresis to prevent detection of unwanted low-level signals. The outputs of the comparators provide full rail logic swings at the frequencies of the incoming DTMF signals.

Figure 3 - Single-Ended Input Configuration

Figure 4 - Differential Input Configuration

| F <sub>LOW</sub> | F <sub>HIGH</sub> | DIGIT | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

|------------------|-------------------|-------|----------------|----------------|----------------|----------------|

| 697              | 1209              | 1     | 0              | 0              | 0              | 1              |

| 697              | 1336              | 2     | 0              | 0              | 1              | 0              |

| 697              | 1477              | 3     | 0              | 0              | 1              | 1              |

| 770              | 1209              | 4     | 0              | 1              | 0              | 0              |

| 770              | 1336              | 5     | 0              | 1              | 0              | 1              |

| 770              | 1477              | 6     | 0              | 1              | 1              | 0              |

| 852              | 1209              | 7     | 0              | 1              | 1              | 1              |

| 852              | 1336              | 8     | 1              | 0              | 0              | 0              |

| 852              | 1477              | 9     | 1              | 0              | 0              | 1              |

| 941              | 1336              | 0     | 1              | 0              | 1              | 0              |

| 941              | 1209              | *     | 1              | 0              | 1              | 1              |

| 941              | 1477              | #     | 1              | 1              | 0              | 0              |

| 697              | 1633              | Α     | 1              | 1              | 0              | 1              |

| 770              | 1633              | В     | 1              | 1              | 1              | 0              |

| 852              | 1633              | С     | 1              | 1              | 1              | 1              |

| 941              | 1633              | D     | 0              | 0              | 0              | 0              |

| 941              | 1633<br>0= LOGIC  |       |                |                | 0              | 0              |

Table 1. Functional Encode/Decode Table

#### MT8888C/MT8888C-1

Following the filter section is a decoder employing digital counting techniques to determine the frequencies of the incoming tones and to verify that they correspond to standard DTMF frequencies. A complex averaging algorithm protects against tone simulation by extraneous signals such as voice while providing tolerance to small frequency deviations and variations. This averaging algorithm has been developed to ensure an optimum combination of immunity to talk-off and tolerance to the presence of interfering frequencies (third tones) and noise. When the detector recognizes the presence of two valid tones (this is referred to as the "signal condition" in some industry specifications) the "Early Steering" (ESt) output will go to an active state. Any subsequent loss of signal condition will cause ESt to assume an inactive state.

#### **Steering Circuit**

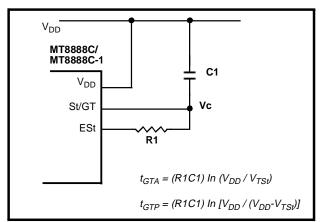

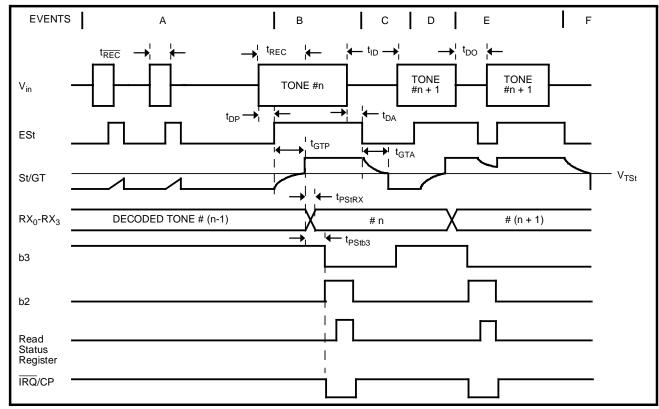

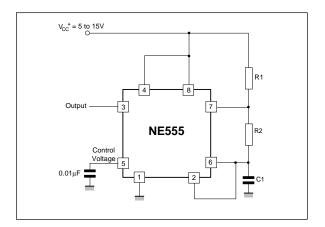

Before registration of a decoded tone pair, the receiver checks for a valid signal duration (referred to as character recognition condition). This check is performed by an external RC time constant driven by ESt. A logic high on ESt causes v<sub>c</sub> (see Figure 5) to rise as the capacitor discharges. Provided that the signal condition is maintained (ESt remains high) for the validation period (t<sub>GTP</sub>), v<sub>c</sub> reaches the threshold (V<sub>TSt</sub>) of the steering logic to register the tone pair, latching its corresponding 4-bit code (see Table 1) into the Receive Data Register. At this point the GT output is activated and drives v<sub>c</sub> to V<sub>DD</sub>. GT continues to drive high as long as ESt remains high. Finally, after a short delay to allow the output latch to settle, the delayed steering output flag goes high, signalling that a received tone pair has been registered. The status of the delayed steering flag can be monitored by checking the appropriate bit in the status register. If Interrupt mode has been selected, the IRQ/CP pin will pull low when the delayed steering flag is active.

The contents of the output latch are updated on an active delayed steering transition. This data is presented to the four bit bidirectional data bus when the Receive Data Register is read. The steering circuit works in reverse to validate the interdigit pause between signals. Thus, as well as rejecting signals too short to be considered valid, the receiver will tolerate signal interruptions (drop out) too short to be considered a valid pause. This facility, together with the capability of selecting the steering time constants externally, allows the designer to tailor performance to meet a wide variety of system requirements.

Figure 5 - Basic Steering Circuit

#### **Guard Time Adjustment**

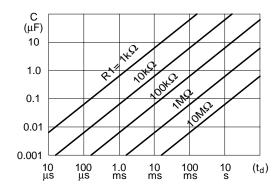

The simple steering circuit shown in Figure 5 is adequate for most applications. Component values are chosen according to the following inequalities (see Figure 7):

$t_{REC} \ge t_{DPmax} + t_{GTPmax} - t_{DAmin}$   $t_{\overline{REC}} \le t_{DPmin} + t_{GTPmin} - t_{DAmax}$   $t_{ID} \ge t_{DAmax} + t_{GTAmax} - t_{DPmin}$   $t_{DO} \le t_{DAmin} + t_{GTAmin} - t_{DPmax}$

The value of  $t_{DP}$  is a device parameter (see AC Electrical Characteristics) and  $t_{REC}$  is the minimum signal duration to be recognized by the receiver. A value for C1 of 0.1  $\mu F$  is recommended for most

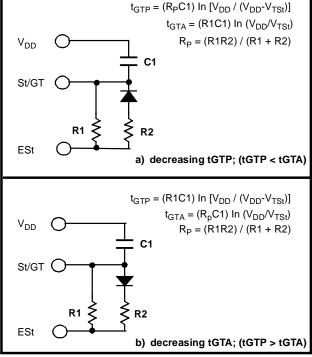

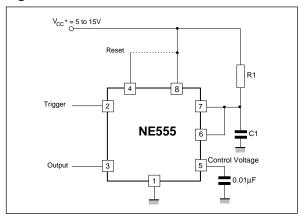

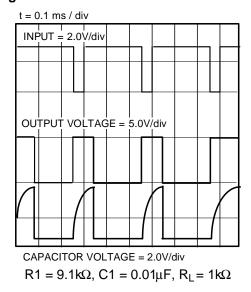

Figure 6 - Guard Time Adjustment

applications, leaving R1 to be selected by the designer. Different steering arrangements may be used to select independent tone present  $(t_{\text{GTP}})$  and tone absent  $(t_{\text{GTA}})$  guard times. This may be necessary to meet system specifications which place both accept and reject limits on tone duration and interdigital pause. Guard time adjustment also allows the designer to tailor system parameters such as talk off and noise immunity.

Increasing  $t_{REC}$  improves talk-off performance since it reduces the probability that tones simulated by speech will maintain a valid signal condition long enough to be registered. Alternatively, a relatively short  $t_{REC}$  with a long  $t_{DO}$  would be appropriate for extremely noisy environments where fast acquisition time and immunity to tone drop-outs are required. Design information for guard time adjustment is shown in Figure 6. The receiver timing is shown in Figure 7 with a description of the events in Figure 9.

#### Call Progress Filter

A call progress mode, using the MT8888C/MT8888C-1, can be selected allowing the detection of various tones, which identify the progress of a telephone call on the network. The call progress tone input and DTMF input are common, however, call progress tones can only be detected when CP

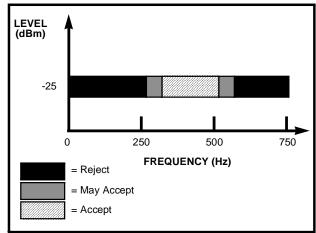

mode has been selected. DTMF signals cannot be detected if CP mode has been selected (see Table 7). Figure 8 indicates the useful detect bandwidth of the call progress filter. Frequencies presented to the input, which are within the 'accept' bandwidth limits of the filter, are hard-limited by a high gain comparator with the IRQ/CP pin serving as the output. The squarewave output obtained from the schmitt trigger can be analyzed by a microprocessor or counter arrangement to determine the nature of the call progress tone being detected. Frequencies which are in the 'reject' area will not be detected and consequently the IRQ/CP pin will remain low.

Figure 8 - Call Progress Response

Figure 7 - Receiver Timing Diagram

#### **EXPLANATION OF EVENTS**

- TONE BURSTS DETECTED, TONE DURATION INVALID, RX DATA REGISTER NOT UPDATED.

- TONE #n DETECTED, TONE DURATION VALID, TONE DECODED AND LATCHED IN RX DATA REGISTER. B)

- C) END OF TONE #n DETECTED, TONE ABSENT DURATION VALID, INFORMATION IN RX DATA REGISTER

- RETAINED UNTIL NEXT VALID TONE PAIR.

- TONE #n+1 DETECTED, TONE DURATION VALID, TONE DECODED AND LATCHED IN RX DATA REGISTER. D)

- ACCEPTABLE DROPOUT OF TONE #n+1, TONE ABSENT DURATION INVALID, DATA REMAINS UNCHANGED. E)

- END OF TONE #n+1 DETECTED, TONE ABSENT DURATION VALID, INFORMATION IN RX DATA REGISTER F)

- RETAINED UNTIL NEXT VALID TONE PAIR.

#### **EXPLANATION OF SYMBOLS**

DTMF COMPOSITE INPUT SIGNAL.  $V_{in}$

EARLY STEERING OUTPUT. INDICATES DETECTION OF VALID TONE FREQUENCIES. ESt STEERING INPUT/GUARD TIME OUTPUT. DRIVES EXTERNAL RC TIMING CIRCUIT. St/GT

$RX_0-RX_3$ 4-BIT DECODED DATA IN RECEIVE DATA REGISTER

DELAYED STEERING. INDICATES THAT VALID FREQUENCIES HAVE BEEN PRESENT/ABSENT FOR THE REQUIRED GUARD TIME THUS CONSTITUTING A VALID SIGNAL. ACTIVE LOW FOR THE DURATION OF A

VALID DTMF SIGNAL.

INDICATES THAT VALID DATA IS IN THE RECEIVE DATA REGISTER. THE BIT IS CLEARED AFTER THE STATUS b2

REGISTER IS READ.

IRO/CP INTERRUPT IS ACTIVE INDICATING THAT NEW DATA IS IN THE RX DATA REGISTER. THE INTERRUPT IS

CLEARED AFTER THE STATUS REGISTER IS READ.

MAXIMUM DTMF SIGNAL DURATION NOT DETECTED AS VALID. t<sub>REC</sub>

MINIMUM DTMF SIGNAL DURATION REQUIRED FOR VALID RECOGNITION. tREC

MINIMUM TIME BETWEEN VALID SEQUENTIAL DTMF SIGNALS.  $t_{ID}$ MAXIMUM ALLOWABLE DROPOUT DURING VALID DTMF SIGNAL.  $t_{DO}$

TIME TO DETECT VALID FREQUENCIES PRESENT.  $t_{DP}$ TIME TO DETECT VALID FREQUENCIES ABSENT.  $t_{DA}$

GUARD TIME. TONE PRESENT.  $t_{GTP}$ GUARD TIME. TONE ABSENT.  $t_{GTA}$

Figure 9 - Description of Timing Events

#### **DTMF** Generator

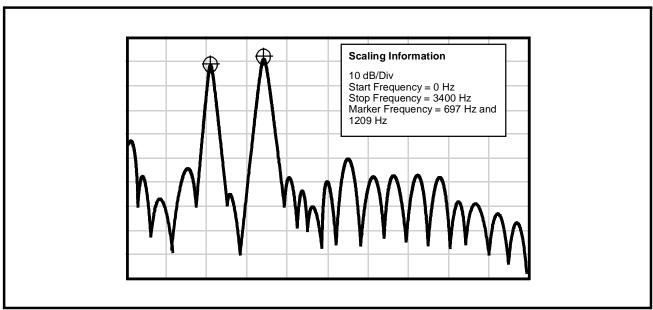

The DTMF transmitter employed in the MT8888C/ MT8888C-1 is capable of generating all sixteen standard DTMF tone pairs with low distortion and high accuracy. All frequencies are derived from an external 3.579545 MHz crystal. The sinusoidal waveforms for the individual tones are digitally synthesized using row and column programmable dividers and switched capacitor D/A converters. The row and column tones are mixed and filtered providing a DTMF signal with low total harmonic distortion and high accuracy. To specify a DTMF signal, data conforming to the encoding format shown in Table 1 must be written to the transmit Data Register. Note that this is the same as the receiver output code. The individual tones which are generated (f<sub>LOW</sub> and f<sub>HIGH</sub>) are referred to as Low Group and High Group tones. As seen from the table, the low group frequencies are 697, 770, 852 and 941 Hz. The high group frequencies are 1209, 1336, 1477 and 1633 Hz. Typically, the high group to low group amplitude ratio (twist) is 2 dB to compensate for high group attenuation on long loops.

The period of each tone consists of 32 equal time segments. The period of a tone is controlled by varying the length of these time segments. During write operations to the Transmit Data Register the 4 bit data on the bus is latched and converted to 2 of 8 coding for use by the programmable divider circuitry. This code is used to specify a time segment length, which will ultimately determine the frequency of the tone. When the divider reaches the appropriate count, as determined by the input code, a reset pulse is issued and the counter starts again. The number of time segments is fixed at 32, however, by varying the segment length as described above the frequency can also be varied. The divider output clocks another counter, which addresses the sinewave lookup ROM.

The lookup table contains codes which are used by the switched capacitor D/A converter to obtain discrete and highly accurate DC voltage levels. Two identical circuits are employed to produce row and column tones, which are then mixed using a low noise summing amplifier. The oscillator described needs no "start-up" time as in other DTMF generators since the crystal oscillator is running continuously thus providing a high degree of tone burst accuracy. A bandwidth limiting filter is incorporated and serves to attenuate distortion products above 8 kHz. It can be seen from Figure 8 that the distortion products are very low in amplitude.

D-6 4-96

Figure 10 - Spectrum Plot

#### **Burst Mode**

In certain telephony applications it is required that DTMF signals being generated are of a specific duration determined either by the particular application or by any one of the exchange transmitter specifications currently existing. Standard DTMF signal timing can be accomplished by making use of the Burst Mode. The transmitter is capable of issuing symmetric bursts/pauses of predetermined duration. This burst/pause duration is 51 ms±1 ms, which is a standard interval for autodialer and central office applications. After the burst/pause has been issued, the appropriate bit is set in the Status Register indicating that the transmitter is ready for more data. The timing described above is available when DTMF mode has been selected. However, when CP mode (Call Progress mode) is selected, the burst/pause duration is doubled to 102 ms ±2 ms. Note that when CP mode and Burst mode have been selected, DTMF tones may be transmitted only and not received. In applications where a non-standard burst/pause time is desirable, a software timing loop or external timer can be used to provide the timing pulses when the burst mode is disabled by enabling and disabling the transmitter.

#### **Single Tone Generation**

A single tone mode is available whereby individual tones from the low group or high group can be generated. This mode can be used for DTMF test equipment applications, acknowledgment tone generation and distortion measurements. Refer to Control Register B description for details.

| ACTIVE | OUTPUT FREQ      | %ERROR    |         |

|--------|------------------|-----------|---------|

| INPUT  | SPECIFIED ACTUAL |           | 70LKKOK |

| L1     | 697              | 699.1     | +0.30   |

| L2     | 770              | 766.2     | -0.49   |

| L3     | 852              | 847.4     | -0.54   |

| L4     | 941              | 941 948.0 |         |

| H1     | 1209             | 1215.9    | +0.57   |

| H2     | 1336             | 1331.7    | -0.32   |

| Н3     | 1477             | 1471.9    | -0.35   |

| H4     | 1633             | 1645.0    | +0.73   |

Table 2. Actual Frequencies Versus Standard Requirements

#### **Distortion Calculations**

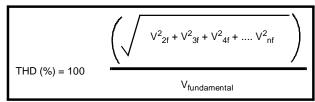

The MT8888C/MT8888C-1 is capable of producing precise tone bursts with minimal error in frequency (see Table 2). The internal summing amplifier is followed by a first-order lowpass switched capacitor filter to minimize harmonic components and intermodulation products. The total harmonic distortion for a *single tone* can be calculated using Equation 1, which is the ratio of the total power of all the extraneous frequencies to the power of the fundamental frequency expressed as a percentage.

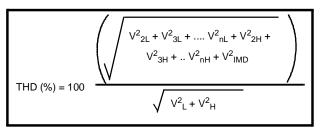

Equation 1. THD (%) For a Single Tone

#### MT8888C/MT8888C-1

The Fourier components of the tone output correspond to  $V_{2f}$ ....  $V_{nf}$  as measured on the output waveform. The total harmonic distortion for a *dual tone* can be calculated using Equation 2.  $V_L$  and  $V_H$  correspond to the low group amplitude and high group amplitude, respectively and  $V_{IMD}^2$  is the sum of all the intermodulation components. The internal switched-capacitor filter following the D/A converter keeps distortion products down to a very low level as shown in Figure 10.

**Equation 2. THD (%) For a Dual Tone**

#### **DTMF Clock Circuit**

The internal clock circuit is completed with the addition of a standard television colour burst crystal. The crystal specification is as follows:

Frequency: 3.579545 MHz

Frequency Tolerance: ±0.1%

Resonance Mode: Parallel

Load Capacitance: 18pF

Maximum Series Resistance:150 ohms

Maximum Drive Level: 2mW

#### e.g. CTS Knights MP036S Toyocom TQC-203-A-9S

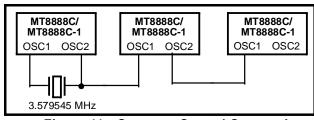

A number of MT8888C/MT8888C-1 devices can be connected as shown in Figure 11 such that only one crystal is required. Alternatively, the OSC1 inputs on all devices can be driven from a TTL buffer with the OSC2 outputs left unconnected.

Figure 11 - Common Crystal Connection

#### **Microprocessor Interface**

The MT8888C/MT8888C-1 incorporates an Intel microprocessor interface which is compatible with fast versions (16 MHz) of the 80C51. No wait cycles need to be inserted.

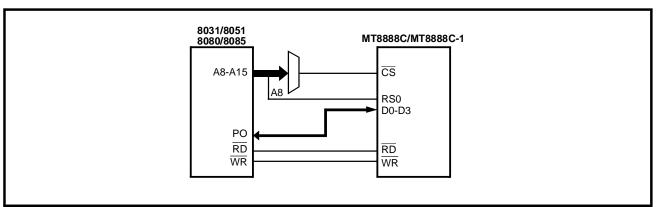

Figures 17 and 18 are the timing diagrams for the Intel 8031, 8051 and 8085 (5 MHz) microcontrollers. By NANDing the address latch enable (ALE) output with the high-byte address (P2) decode output, CS is generated. Figure 12 summarizes the connection of these Intel processors to the MT8888C/MT8888C-1 transceiver.

The microprocessor interface provides access to five internal registers. The read-only Receive Data Register contains the decoded output of the last valid DTMF digit received. Data entered into the write-only Transmit Data Register will determine which tone pair is to be generated (see Table 1 for coding details). Transceiver control is accomplished with two control registers (see Tables 6 and 7), CRA and CRB, which have the same address. A write operation to CRB is executed by first setting the most significant bit (b3) in CRA. The following write operation to the same address will then be directed to CRB, and subsequent write cycles will be directed back to CRA. The read-only status register indicates the current transceiver state (see Table 8).

A software reset must be included at the beginning of all programs to initialize the control registers upon power-up or power reset (see Figure 17). Refer to Tables 4-7 for bit descriptions of the two control registers.

The multiplexed IRQ/CP pin can be programmed to generate an interrupt upon validation of DTMF signals or when the transmitter is ready for more data (burst mode only). Alternatively, this pin can be configured to provide a squarewave output of the call progress signal. The IRQ/CP pin is an open drain output and requires an external pull-up resistor (see Figure 13).

| RS0 | WR | RD | FUNCTION                           |

|-----|----|----|------------------------------------|

| 0   | 0  | 1  | Write to Transmit<br>Data Register |

| 0   | 1  | 0  | Read from Receive<br>Data Register |

| 1   | 0  | 1  | Write to Control Register          |

| 1   | 1  | 0  | Read from Status Register          |

Table 3. Internal Register Functions

| b3   | b2  | b1      | b0   |

|------|-----|---------|------|

| RSEL | IRQ | CP/DTMF | TOUT |

Table 4. CRA Bit Positions

| b3  | b2  | b1   | b0              |

|-----|-----|------|-----------------|

| C/R | S/D | TEST | BURST<br>ENABLE |

Table 5. CRB Bit Positions

| BIT | NAME    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b0  | TOUT    | Tone Output Control. A logic high enables the tone output; a logic low turns the tone output off. This bit controls all transmit tone functions.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| b1  | CP/DTMF | Call Progress or DTMF Mode Select. A logic high enables the receive call progress mode; a logic low enables DTMF mode. In DTMF mode the device is capable of receiving and transmitting DTMF signals. In CP mode a rectangular wave representation of the received tone signal will be present on the IRQ/CP output pin if IRQ has been enabled (control register A, b2=1). In order to be detected, CP signals must be within the bandwidth specified in the AC Electrical Characteristics for Call Progress.  Note: DTMF signals cannot be detected when CP mode is selected. |

| b2  | IRQ     | Interrupt Enable. A logic high enables the interrupt function; a logic low de-activates the interrupt function. When IRQ is enabled and DTMF mode is selected (control register A, b1=0), the IRQ/CP output pin will go low when either 1) a valid DTMF signal has been received for a valid guard time duration, or 2) the transmitter is ready for more data (burst mode only).                                                                                                                                                                                               |

| b3  | RSEL    | Register Select. A logic high selects control register B for the next write cycle to the control register address. After writing to control register B, the following control register write cycle will be directed to control register A.                                                                                                                                                                                                                                                                                                                                      |

Table 6. Control Register A Description

| ВІТ | NAME  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b0  | BURST | Burst Mode Select. A logic high de-activates burst mode; a logic low enables burst mode. When activated, the digital code representing a DTMF signal (see Table 1) can be written to the transmit register, which will result in a transmit DTMF tone burst and pause of equal durations (typically 51 msec.). Following the pause, the status register will be updated (b1 - Transmit Data Register Empty), and an interrupt will occur if the interrupt mode has been enabled. |

|     |       | When CP mode (control register A, b1) is enabled the normal tone burst and pause durations are extended from a typical duration of 51 msec to 102 msec.                                                                                                                                                                                                                                                                                                                          |

|     |       | When BURST is high (de-activated) the transmit tone burst duration is determined by the TOUT bit (control register A, b0).                                                                                                                                                                                                                                                                                                                                                       |

| b1  | TEST  | Test Mode Control. A logic high enables the test mode; a logic low de-activates the test mode. When TEST is enabled and DTMF mode is selected (control register A, b1=0), the signal present on the IRQ/CP pin will be analogous to the state of the DELAYED STEERING bit of the status register (see Figure 7, signal b3).                                                                                                                                                      |

| b2  | S/D   | Single or Dual Tone Generation. A logic high selects the single tone output; a logic low selects the dual tone (DTMF) output. The single tone generation function requires further selection of either the row or column tones (low or high group) through the C/R bit (control register B, b3).                                                                                                                                                                                 |

| b3  | C/R   | Column or Row Tone Select. A logic high selects a column tone output; a logic low selects a row tone output. This function is used in conjunction with the S/D bit (control register B, b2).                                                                                                                                                                                                                                                                                     |

Table 7. Control Register B Description

| BIT | NAME                                           | STATUS FLAG SET                                                      | STATUS FLAG CLEARED                                              |

|-----|------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------|

| b0  | IRQ                                            | Interrupt has occurred. Bit one (b1) or bit two (b2) is set.         | Interrupt is inactive. Cleared after Status Register is read.    |

| b1  | TRANSMIT DATA REGISTER EMPTY (BURST MODE ONLY) | Pause duration has terminated and transmitter is ready for new data. | Cleared after Status Register is read or when in non-burst mode. |

| b2  | RECEIVE DATA REGISTER FULL                     | Valid data is in the Receive Data Register.                          | Cleared after Status Register is read.                           |

| b3  | DELAYED STEERING                               | Set upon the valid detection of the absence of a DTMF signal.        | Cleared upon the detection of a valid DTMF signal.               |

Table 8. Status Register Description

Figure 12 - MT8888C Interface Connections for Various Intel Micros

Figure 13 - Application Circuit (Single-Ended Input)

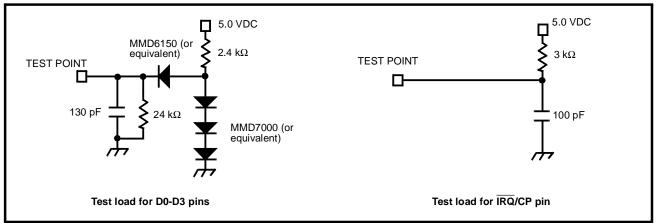

Figure 14 - Test Circuits

#### **INITIALIZATION PROCEDURE**

A software reset must be included at the beginning of all programs to initialize the control registers after power up. The initialization procedure should be implemented 100ms after power up.

| Description:                 | Control |    |    | Data       |    |    |    |

|------------------------------|---------|----|----|------------|----|----|----|

|                              | RS0     | WR | RD | <b>b</b> 3 | b2 | b1 | b0 |

| Read Status Register         | 1       | 1  | 0  | Χ          | Χ  | Χ  | Χ  |

| 2) Write to Control Register | 1       | 0  | 1  | 0          | 0  | 0  | 0  |

| 3) Write to Control Register | 1       | 0  | 1  | 0          | 0  | 0  | 0  |

| 4) Write to Control Register | 1       | 0  | 1  | 1          | 0  | 0  | 0  |

| 5) Write to Control Register | 1       | 0  | 1  | 0          | 0  | 0  | 0  |

| 6) Read Status Register      | 1       | 1  | 0  | Χ          | Χ  | Χ  | Χ  |

#### TYPICAL CONTROL SEQUENCE FOR BURST MODE APPLICATIONS

Transmit DTMF tones of 50 ms burst/50 ms pause and Receive DTMF Tones.

#### Sequence:

|    |                                                     | RS0       | WR       | RD | b3 | b2 | b1 | b0 |

|----|-----------------------------------------------------|-----------|----------|----|----|----|----|----|

| 1) | Write to Control Register A                         | 1         | 0        | 1  | 1  | 1  | 0  | 1  |

|    | (tone out, DTMF, IRQ, Select Control Register       | B)        |          |    |    |    |    |    |

| 2) | Write to Control Register B                         | 1         | 0        | 1  | 0  | 0  | 0  | 0  |

|    | (burst mode)                                        |           |          |    |    |    |    |    |

| 3) | Write to Transmit Data Register                     | 0         | 0        | 1  | 0  | 1  | 1  | 1  |

|    | (send a digit 7)                                    |           |          |    |    |    |    |    |

| 4) | Wait for an interrupt or poll Status Register       |           |          |    |    |    |    |    |

| 5) | Read the Status Register                            | 1         | 1        | 0  | X  | Χ  | Χ  | Χ  |

|    |                                                     |           |          |    |    |    |    |    |

|    | -if bit 1 is set, the Tx is ready for the next tone | , in whi  | ch case  |    |    |    |    |    |

|    | Write to Transmit Register                          | 0         | 0        | 1  | 0  | 1  | 0  | 1  |

|    | (send a digit 5)                                    |           |          |    |    |    |    |    |

|    |                                                     |           |          |    |    |    |    |    |

|    | -if bit 2 is set, a DTMF tone has been received     | d, in whi | ch case. |    |    |    |    |    |

|    | Read the Receive Data Register                      | 0         | 1        | 0  | Х  | X  | Х  | Х  |

|    | -if both bits are set                               |           |          |    |    |    |    |    |

|    | Read the Receive Data Register                      | 0         | 1        | 0  | Х  | Χ  | Χ  | X  |

|    | Write to Transmit Data Register                     | 0         | 0        | 1  | 0  | 1  | 0  | 1  |

|    | Willo to Hallollit Data Register                    | U         | U        |    | U  |    | U  |    |

NOTE: IN THE TX BURST MODE, STATUS REGISTER BIT 1 WILL NOT BE SET UNTIL 100 ms ( $\pm 2$  ms) AFTER THE DATA IS WRITTEN TO THE TX DATA REGISTER. IN EXTENDED BURST MODE THIS TIME WILL BE DOUBLED TO 200 ms ( $\pm 4$  ms).

Figure 15 - Application Notes

## LAMPIRAN E

**DATASHEET NE555**

#### NE555 SA555 - SE555

#### GENERAL PURPOSE SINGLE BIPOLAR TIMERS

- LOW TURN OFF TIME

- MAXIMUM OPERATING FREQUENCY GREATER THAN 500kHz

- TIMING FROM MICROSECONDS TO HOURS

- OPERATES IN BOTH ASTABLE AND MONOSTABLE MODES

- HIGH OUTPUT CURRENT CAN SOURCE OR SINK 200mA

- ADJUSTABLE DUTY CYCLE

- TTL COMPATIBLE

- TEMPERATURE STABILITY OF 0.005% PER°C

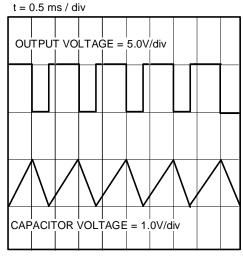

#### **DESCRIPTION**

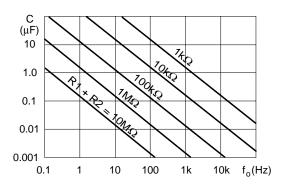

The NE555 monolithic timing circuit is a highly stable controller capable of producing accurate time delays or oscillation. In the time delay mode of operation, the time is precisely controlled by one external resistor and capacitor. For a stable operation as an oscillator, the free running frequency and the duty cycle are both accurately controlled with two external resistors and one capacitor. The circuit may be triggered and reset on falling waveforms, and the output structure can source or sink up to 200mA. The NE555 is available in plastic and ceramic minidip package and in a 8-lead micropackage and in metal can package version.

#### **ORDER CODES**

| Part   | Temperature  | Pack<br>N | kage |  |

|--------|--------------|-----------|------|--|

| Number | Range        | N         | D    |  |

| NE555  | 0°C, 70°C    | •         | •    |  |

| SA555  | –40°C, 105°C | •         | •    |  |

| SE555  | –55°C, 125°C | •         | •    |  |

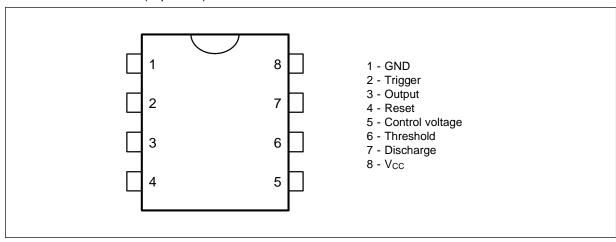

#### PIN CONNECTIONS (top view)

July 1998 1/10

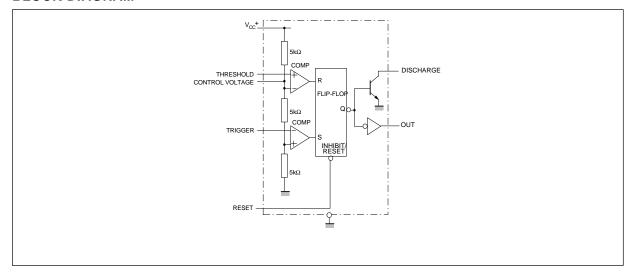

#### **BLOCK DIAGRAM**

#### **SCHEMATIC DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol            | Parameter Value                                                    |                                     | Unit |

|-------------------|--------------------------------------------------------------------|-------------------------------------|------|

| V <sub>cc</sub>   | Supply Voltage                                                     | 18                                  | V    |

| T <sub>oper</sub> | Operating Free Air Temperature Range for NE555 for SA555 for SE555 | 0 to 70<br>-40 to 105<br>-55 to 125 | °C   |

| Tj                | Junction Temperature                                               | 150                                 | °C   |

| T <sub>stg</sub>  | Storage Temperature Range                                          | -65 to 150                          | °C   |

2/10

E-2

## **OPERATING CONDITIONS**

| Symbol                                                                     | Parameter             | SE555     | NE555 - SA555   | Unit |

|----------------------------------------------------------------------------|-----------------------|-----------|-----------------|------|

| V <sub>CC</sub>                                                            | Supply Voltage        | 4.5 to 18 | 4.5 to 18       | ٧    |

| V <sub>th</sub> , V <sub>trig</sub> , V <sub>cl</sub> , V <sub>reset</sub> | Maximum Input Voltage | Vcc       | V <sub>CC</sub> | ٧    |

## **ELECTRICAL CHARACTERISTICS**

$T_{amb} = +25^{\circ}C$ ,  $V_{CC} = +5V$  to +15V (unless otherwise specified)

| Symbol             | Parameter                                                                                                                                                                                                                                                         | SE555       |                                       |                                   | NE555 - SA555 |                                       |                                    | Unit               |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------------------|-----------------------------------|---------------|---------------------------------------|------------------------------------|--------------------|

|                    |                                                                                                                                                                                                                                                                   | Min.        | Тур.                                  | Max.                              | Min.          | Тур.                                  | Max.                               |                    |

| Icc                | Supply Current (R <sub>L</sub> $\infty$ ) (- note 1)<br>Low State $V_{CC} = +5V$<br>$V_{CC} = +15V$<br>High State $V_{CC} = 5V$                                                                                                                                   |             | 3<br>10<br>2                          | 5<br>12                           |               | 3<br>10<br>2                          | 6<br>15                            | mA                 |

|                    | Timing Error (monostable) $(R_A = 2k \text{ to } 100k\Omega, C = 0.1\mu\text{F})$ Initial Accuracy - (note 2) Drift with Temperature Drift with Supply Voltage                                                                                                    |             | 0.5<br>30<br>0.05                     | 2<br>100<br>0.2                   |               | 1<br>50<br>0.1                        | 3<br>0.5                           | %<br>ppm/°C<br>%/V |

|                    | Timing Error (astable) $ \begin{array}{l} \text{(R}_A,R_B=1 k \Omega \text{ to } 100 k \Omega,C=0.1 \mu F,\\ \text{V}_{CC}=+15 \text{V)} \\ \text{Initial Accuracy - (note 2)} \\ \text{Drift with Temperature} \\ \text{Drift with Supply Voltage} \end{array} $ |             | 1.5<br>90<br>0.15                     |                                   |               | 2.25<br>150<br>0.3                    |                                    | %<br>ppm/°C<br>%/V |

| $V_{CL}$           | Control Voltage level $V_{CC} = +15V$ $V_{CC} = +5V$                                                                                                                                                                                                              | 9.6<br>2.9  | 10<br>3.33                            | 10.4<br>3.8                       | 9<br>2.6      | 10<br>3.33                            | 11<br>4                            | V                  |

| V <sub>th</sub>    | Threshold Voltage $V_{CC} = +15V$ $V_{CC} = +5V$                                                                                                                                                                                                                  | 9.4<br>2.7  | 10<br>3.33                            | 10.6<br>4                         | 8.8<br>2.4    | 10<br>3.33                            | 11.2<br>4.2                        | V                  |

| I <sub>th</sub>    | Threshold Current - (note 3)                                                                                                                                                                                                                                      |             | 0.1                                   | 0.25                              |               | 0.1                                   | 0.25                               | μΑ                 |

| V <sub>trig</sub>  | Trigger Voltage  V <sub>CC</sub> = +15V  V <sub>CC</sub> = +5V                                                                                                                                                                                                    | 4.8<br>1.45 | 5<br>1.67                             | 5.2<br>1.9                        | 4.5<br>1.1    | 5<br>1.67                             | 5.6<br>2.2                         | V                  |