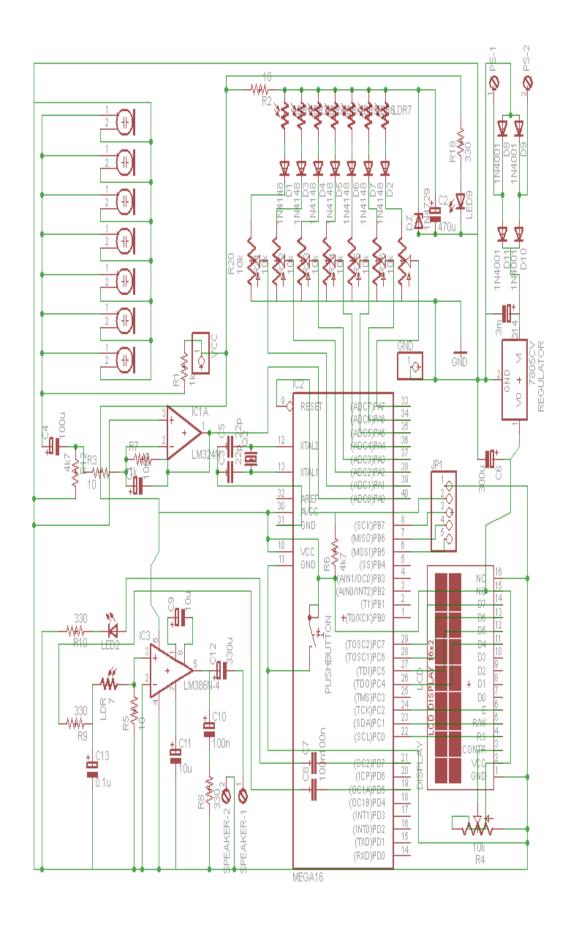

# LAMPIRAN A SKEMATIK

# LAMPIRAN B1 DATA SHEET ATMEGA16

#### **Features**

- High-performance, Low-power AVR® 8-bit Microcontroller

Advanced RISC Architecture

- Peripheral Features

- eripheral relatures

Two 8-bit Timer/Counters with Separate Prescalers and Compare Modes

One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture

- Real Time Counter with Separate Oscillator

- Four PWM Channels

- Real Time Counter with Separate Oscillator

Four PWM Channels

8-channel, 10-bit ADC

8 Single-ended Channels

7 Differential Channels in TQFP Package Only

2 Differential Channels with Programmable Gain at 1x, 10x, or 200x

Byte-oriented Two-wire Serial Interface

Programmable Serial USART

Master/Slave SPI Serial Interface

Programmable Watchdog Timer with Separate On-chip Oscillator

On-chip Analog Comparator

Special Microcontroller Features

Power-on Reset and Programmable Brown-out Detection

Internal Calibrated RC Oscillator

External and Internal Interrupt Sources

Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby and Extended Standby

I/O and Packages

32 Programmable I/O Lines

40-pin PDIP, 44-lead TQFP, and 44-pad QFN/MLF

Operating Voltages

- Operating Voltages

- 2.7 5.5V for ATmega16L

- 4.5 5.5V for ATmega16

Speed Grades

- 0 8 MHz for ATmega16L

- O 16 MHz for ATmega16

Power Consumption @ 1 MHz, 3V, and 25°C for ATmega16L

Active: 1.1 mA

I die Mode: 0.35 mA

- Power-down Mode: < 1 µA

8-bit **AVR**® Microcontroller with 16K Bytes In-System **Programmable** Flash

ATmega16 ATmega16L

#### Pin Figure 1. Pinout ATmega16 Configurations

#### Overview

The ATmega16 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega16 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

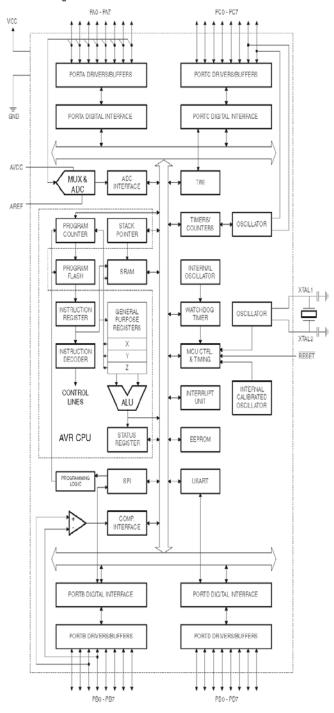

#### **Block Diagram**

Figure 2. Block Diagram

#### **AVR CPU Core**

#### Introduction

This section discusses the AVR core architecture in general. The main function of the CPU core is to ensure correct program execution. The CPU must therefore be able to access memories, perform calculations, control peripherals, and handle interrupts.

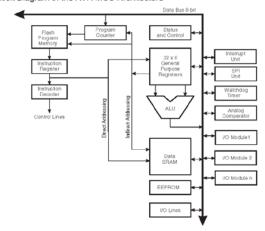

#### Architectural Overview

Figure 3. Block Diagram of the AVR MCU Architecture

In order to maximize performance and parallelism, the AVR uses a Harvard architecture — with separate memories and buses for program and data. Instructions in the program memory are executed with a single level pipelining. While one instruction is being executed, the next instruction is per-fetched from the program memory. This concept enables instructions to be executed in every clock cycle. The program memory is In-System Reprogrammable Flash memory.

The fast-access Register File contains 32 x 8-bit general purpose working registers with a single clock cycle access time. This allows single-cycle Arithmetic Logic Unit (ALU) operation. In a typical ALU operation, two operands are output from the Register File, the operation is executed, and the result is stored back in the Register File – in one clock cycle.

Six of the 32 registers can be used as three 16-bit indirect address register pointers for Data Space addressing – enabling efficient address calculations. One of the these address pointers can also be used as an address pointer for look up tables in Flash Program memory. These added function registers are the 16-bit X-, Y-, and Z-register, described later in this section.

The ALU supports arithmetic and logic operations between registers or between a constant and a register. Single register operations can also be executed in the ALU. After an arithmetic operation, the Status Register is updated to reflect information about the result of the operation.

Program flow is provided by conditional and unconditional jump and call instructions, able to directly address the whole address space. Most AVR instructions have a single 16-bit word format. Every program memory address contains a 16- or 32-bit instruction.

Program Flash memory space is divided in two sections, the Boot program section and the Application Program section. Both sections have dedicated Lock bits for write and read/write protection. The SPM instruction that writes into the Application Flash memory section must reside in the Boot Program section.

During interrupts and subroutine calls, the return address Program Counter (PC) is stored on the Stack. The Stack is effectively allocated in the general data SRAM, and consequently the Stack size is only limited by the total SRAM size and the usage of the SRAM. All user programs must initialize the SP in the reset routine (before subroutines or interrupts are executed). The Stack Pointer SP is read/write accessible in the I/O space. The data SRAM can easily be accessed through the five different addressing modes supported in the AVR architecture.

The memory spaces in the AVR architecture are all linear and regular memory maps.

A flexible interrupt module has its control registers in the I/O space with an additional global interrupt enable bit in the Status Register. All interrupts have a separate interrupt vector in the interrupt vector table. The interrupts have priority in accordance with their interrupt vector position. The lower the interrupt vector address, the higher the priority.

The I/O memory space contains 64 addresses for CPU peripheral functions as Control Registers, SPI, and other I/O functions. The I/O Memory can be accessed directly, or as the Data Space locations following those of the Register File, \$20 - \$5F.

#### ALU – Arithmetic Logic Unit

The high-performance AVR ALU operates in direct connection with all the 32 general purpose working registers. Within a single clock cycle, arithmetic operations between general purpose registers or between a register and an immediate are executed. The ALU operations are divided into three main categories – arithmetic, logical, and bit-functions. Some implementations of the architecture also provide a powerful multiplier supporting both signed/unsigned multiplication and fractional format. See the "Instruction Set" section for a detailed description.

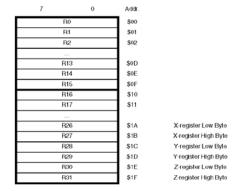

#### General Purpose Register File

The Register File is optimized for the AVR Enhanced RISC instruction set. In order to achieve the required performance and flexibility, the following input/output schemes are supported by the Register File:

- One 8-bit output operand and one 8-bit result input

- Two 8-bit output operands and one 8-bit result input

- · Two 8-bit output operands and one 16-bit result input

- One 16-bit output operand and one 16-bit result input

Figure 4 shows the structure of the 32 general purpose working registers in the CPU.

Figure 4. AVR CPU General Purpose Working Registers

General

Purpose

Working Registers

Most of the instructions operating on the Register File have direct access to all registers, and most of them are single cycle instructions.

As shown in Figure 4, each register is also assigned a data memory address, mapping them directly into the first 32 locations of the user Data Space. Although not being physically implemented as SRAM locations, this memory organization provides great flexibility in access of the registers, as the Y-, Y-, and Z-pointer Registers can be set to index any register in the file.

#### AVR ATmega16 Memories

This section describes the different memories in the ATmega16. The AVR architecture has two main memory spaces, the Data Memory and the Program Memory space. In addition, the ATmega16 features an EEPROM Memory for data storage. All three memory spaces are linear and regular.

In-System Reprogrammable Flash Program Memory The ATmega16 contains 16K bytes On-chip In-System Reprogrammable Flash memory for program storage. Since all AVR instructions are 16 or 32 bits wide, the Flash is organized as 8K x 16. For software security, the Flash Program memory space is divided into two sections, Boot Program section and Application Program section.

The Flash memory has an endurance of at least 10,000 write/erase cycles. The ATmega16 Program Counter (PC) is 13 bits wide, thus addressing the 8K program memory locations. The operation of Boot Program section and associated Boot Lock bits for software protection are described in detail in "Boot Loader Support – Read-While-Write Self-Programming" on page 246, "Memory Programming" on page 259 contains a detailed description on Flash data serial downloading using the SPI pins or the JTAG interface.

Constant tables can be allocated within the entire program memory address space (see the LPM – Load Program Memory Instruction Description).

Timing diagrams for instruction fetch and execution are presented in "Instruction Execution Timing" on page 13.

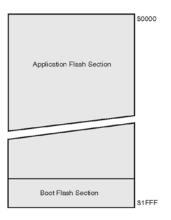

Figure 8. Program Memory Map

#### SRAM Data Memory

Figure 9 shows how the ATmega16 SRAM Memory is organized.

The lower 1120 Data Memory locations address the Register File, the I/O Memory, and the internal data SRAM. The first 96 locations address the Register File and I/O Memory, and the next 1024 locations address the internal data SRAM.

The five different addressing modes for the data memory cover: Direct, Indirect with Displacement, Indirect, Indirect with Pre-decrement, and Indirect with Post-increment. In the Register File, registers R26 to R31 feature the indirect addressing pointer registers.

The direct addressing reaches the entire data space

The Indirect with Displacement mode reaches 63 address locations from the base address given by the Y- or Z-register.

When using register indirect addressing modes with automatic pre-decrement and post-increment, the address registers X, Y, and Z are decremented or incremented.

The 32 general purpose working registers, 64 I/O Registers, and the 1024 bytes of internal data SRAM in the ATmega16 are all accessible through all these addressing modes. The Register File is described in "General Purpose Register File" on page 11.

Figure 9. Data Memory Map

| Register File | Data Address Space |

|---------------|--------------------|

| R0            | \$0000             |

| R1            | \$0001             |

| R2            | \$0002             |

|               |                    |

| R29           | \$001D             |

| R30           | \$001E             |

| R31           | \$001F             |

| I/O Registers |                    |

| \$00          | \$0020             |

| \$01          | \$0021             |

| \$02          | \$0022             |

|               |                    |

| \$3D          | \$005D             |

| \$3E          | \$005E             |

| \$3F          | \$005F             |

|               | Internal SRAM      |

|               | \$0060             |

|               | \$0061             |

|               |                    |

|               | \$045E             |

|               | \$045F             |

#### 16-bit Timer/Counter1

The 16-bit Timer/Counter unit allows accurate program execution timing (event management), wave generation, and signal timing measurement. The main features are:

- True 16-bit Design (i.e., Allows 16-bit PWM)

- Two Independent Output Compare Units

- Double Buffered Output Compare Registers

- One Input Capture Unit

- · Input Capture Noise Canceler

- . Clear Timer on Compare Match (Auto Reload)

- Glitch-free, Phase Correct Pulse Width Modulator (PWM)

- Variable PWM Period

- · Frequency Generator

- External Event Counter

- Four Independent Interrupt Sources (TOV1, OCF1A, OCF1B, and ICF1)

#### Overview

Most register and bit references in this section are written in general form. A lower case "n" replaces the Timer/Counter number, and a lower case "x" replaces the output compare unit. However, when using the register or bit defines in a program, the precise form must be used (i.e., TCNT1 for accessing Timer/Counter1 counter value and so on).

A simplified block diagram of the 16-bit Timer/Counter is shown in Figure 40. For the actual placement of I/O pins, refer to Figure 1 on page 2. CPU accessible I/O Registers, including I/O bits and I/O pins, are shown in bold. The device specific I/O Register and bit locations are listed in the "16-bit Timer/Counter Register Description" on page 110.

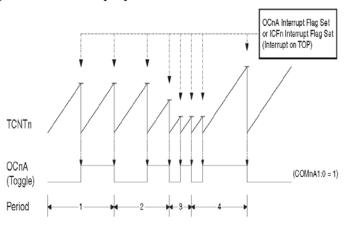

Clear Timer on Compare Match (CTC) Mode In Clear Timer on Compare or CTC mode (WGM13:0 = 4 or 12), the OCR1A or ICR1 Register are used to manipulate the counter resolution. In CTC mode the counter is cleared to zero when the counter value (TCNT1) matches either the OCR1A (WGM13:0 = 4) or the ICR1 (WGM13:0 = 12). The OCR1A or ICR1 define the top value for the counter, hence also its resolution. This mode allows greater control of the compare match output frequency. It also simplifies the operation of counting external events.

The timing diagram for the CTC mode is shown in Figure 45. The counter value (TCNT1) increases until a compare match occurs with either OCR1A or ICR1, and then counter (TCNT1) is cleared.

Figure 45. CTC Mode, Timing Diagram

An interrupt can be generated at each time the counter value reaches the TOP value by either using the OCF1A or ICF1 Flag according to the register used to define the TOP value. If the interrupt is enabled, the interrupt handler routine can be used for updating the TOP value. However, changing the TOP to a value close to BOTTOM when the counter is running with none or a low prescaler value must be done with care since the CTC mode does not have the double buffering feature. If the new value written to OCR1A or ICR1 is lower than the current value of TCNT1, the counter will miss the compare match. The counter will then have to count to its maximum value (0xFFFF) and wrap around starting at 0x0000 before the compare match can occur. In many cases this feature is not desirable. An alternative will then be to use the fast PWM mode using OCR1A for defining TOP (WGM13:0 = 15) since the OCR1A then will be double buffered.

For generating a waveform output in CTC mode, the OC1A output can be set to toggle its logical level on each compare match by setting the compare output mode bits to toggle mode (COM1A1:0 = 1). The OC1A value will not be visible on the port pin unless the data direction for the pin is set to output (DDR\_OC1A = 1). The waveform generated will have a maximum frequency of  $f_{\rm OC1A} = f_{\rm olk\_IIO}/2$  when OCR1A is set to zero (0x0000). The waveform frequency is defined by the following equation:

$$f_{OCnA} = \frac{f_{\text{clk\_I/O}}}{2 \cdot N \cdot (1 + OCRnA)}$$

The N variable represents the prescaler factor (1, 8, 64, 256, or 1024).

As for the Normal mode of operation, the TOV1 Flag is set in the same timer clock cycle that the counter counts from MAX to 0x0000.

8-bit

Timer/Counter2 is a general purpose, single compare unit, 8-bit Timer/Counter module. The main features are:

Timer/Counter2 with PWM and

- . Single Compare unit Counter

- . Clear Timer on Compare Match (Auto Reload)

### Asynchronous Operation

- . Glitch-free, Phase Correct Pulse Width Modulator (PWM)

- · Frequency Generator

- 10-bit Clock Prescaler

- . Overflow and Compare Match Interrupt Sources (TOV2 and OCF2)

- . Allows clocking from External 32 kHz Watch Crystal Independent of the I/O Clock

#### Overview

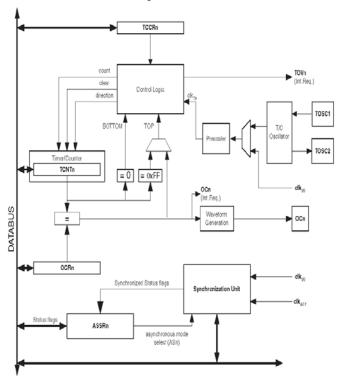

A simplified block diagram of the 8-bit Timer/Counter is shown in Figure 53. For the actual placement of I/O pins, refer to "Pinout ATmega16" on page 2. CPU accessible I/O Registers, including I/O bits and I/O pins, are shown in bold. The device-specific I/O Register and bit locations are listed in the "8-bit Timer/Counter Register Description" on page 128.

Figure 53. 8-bit Timer/Counter Block Diagram

#### Registers

The Timer/Counter (TCNT2) and Output Compare Register (OCR2) are 8-bit registers. Interrupt request (shorten as Int.Req.) signals are all visible in the Timer Interrupt Flag Register (TIFR). All interrupts are individually masked with the Timer Interrupt Mask Register (TIMSK). TIFR and TIMSK are not shown in the figure since these registers are shared by other timer units.

The Timer/Counter can be clocked internally, via the prescaler, or asynchronously clocked from the TOSC1/2 pins, as detailed later in this section. The asynchronous operation is controlled by the Asynchronous Status Register (ASSR). The Clock Select logic block controls which clock source the Timer/Counter uses to increment (or decrement) its value. The Timer/Counter is inactive when no clock source is selected. The output from the Clock Select logic is referred to as the timer clock (clk $_{12}$ ).

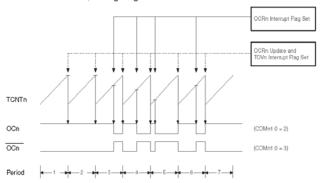

#### Fast PWM Mode

The fast Pulse Width Modulation or fast PWM mode (WGM21:0 = 3) provides a high frequency PWM waveform generation option. The fast PWM differs from the other PWM option by its single-slope operation. The counter counts from BOTTOM to MAX then restarts from BOTTOM. In onn-inverting Compare Output mode, the Output Compare (OC2) is cleared on the compare match between TCNT2 and OCR2, and set at BOTTOM. In inverting Compare Output mode, the output is set on compare match and cleared at BOTTOM. Due to the single-slope operation, the operating frequency of the fast PWM mode can be twice as high as the phase correct PWM mode that uses dual-slope operation. This high frequency makes the fast PWM mode well suited for power regulation, rectification, and DAC applications. High frequency allows physically small sized external components (coils, capacitors), and therefore reduces total system cost.

In fast PWM mode, the counter is incremented until the counter value matches the MAX value. The counter is then cleared at the following timer clock cycle. The timing diagram for the fast PWM mode is shown in Figure 58. The TCNT2 value is in the timing diagram shown as a histogram for illustrating the single-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT2 slopes represent compare matches between OCR2 and TCNT2.

Figure 58. Fast PWM Mode, Timing Diagram

The Timer/Counter Overflow Flag (TOV2) is set each time the counter reaches MAX. If the interrupt is enabled, the interrupt handler routine can be used for updating the compare value.

In fast PWM mode, the compare unit allows generation of PWM waveforms on the OC2 pin. Setting the COM21:0 bits to 2 will produce a non-inverted PWM and an inverted PWM output can be generated by setting the COM21:0 to 3 (see Table 52 on page 129). The actual OC2 value will only be visible on the port pin if the data direction for the port pin is set as output. The PWM waveform is generated by setting (or clearing) the OC2 Register at the compare match between OCR2 and TCNT2, and clearing (or setting) the OC2 Register at the timer clock cycle the counter is cleared (changes from MAX to BOTTOM).

The PWM frequency for the output can be calculated by the following equation:

$$f_{OCnPWM} = \frac{f_{\text{clk\_I/O}}}{N.256}$$

The N variable represents the prescale factor (1, 8, 32, 64, 128, 256, or 1024).

The extreme values for the OCR2 Register represent special cases when generating a PWM waveform output in the fast PWM mode. If the OCR2 is set equal to BOTTOM, the output will be a narrow spike for each MAX+1 timer clock cycle. Setting the OCR2 equal to MAX will result in a constantly high or low output (depending on the polarity of the output set by the COM21:0 bits.)

A frequency (with 50% duty cycle) waveform output in fast PWM mode can be achieved by setting OC2 to toggle its logical level on each compare match (COM21:0 = 1). The waveform generated will have a maximum frequency of  $f_{\text{oc2}} = f_{\text{clk\_IIO}}/2$  when OCR2 is set to zero. This feature is similar to the OC2 toggle in CTC mode, except the double buffer feature of the output compare unit is enabled in the fast PWM mode.

# Analog to Digital Converter

#### **Features**

- 10-bit Resolution

- · 0.5 LSB Integral Non-linearity

- ±2 LSB Absolute Accuracy

- 13 260 µs Conversion Time

- Up to 15 kSPS at Maximum Resolution

- . 8 Multiplexed Single Ended Input Channels

- 7 Differential Input Channels

- 2 Differential Input Channels with Optional Gain of 10x and 200x

- Optional Left adjustment for ADC Result Readout

- 0 V<sub>CC</sub> ADC Input Voltage Range

- Selectable 2.56V ADC Reference Voltage

- Free Running or Single Conversion Mode

- ADC Start Conversion by Auto Triggering on Interrupt Sources

- Interrupt on ADC Conversion Complete

- Sleep Mode Noise Canceler

The ATmega16 features a 10-bit successive approximation ADC. The ADC is connected to an 8-channel Analog Multiplexer which allows 8 single-ended voltage inputs constructed from the pins of Port A. The single-ended voltage inputs refer to 0V (GND).

The device also supports 16 differential voltage input combinations. Two of the differential inputs (ADC1, ADC0 and ADC3, ADC2) are equipped with a programmable gain stage, providing amplification steps of 0 dB (1x), 20 dB (10x), or 46 dB (200x) on the differential input voltage before the A/D conversion. Seven differential analog input channels share a common negative terminal (ADC1), while any other ADC input can be selected as the positive input terminal. If 1x or 10x gain is used, 8-bit resolution can be expected. If 200x gain is used, 7-bit resolution can be expected.

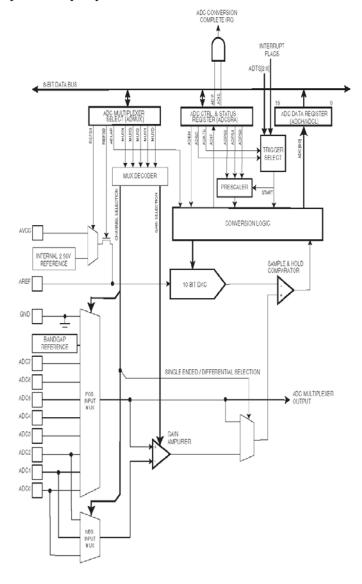

The ADC contains a Sample and Hold circuit which ensures that the input voltage to the ADC is held at a constant level during conversion. A block diagram of the ADC is shown in Figure 98.

The ADC has a separate analog supply voltage pin, AVCC. AVCC must not differ more than  $\pm 0.3$  V from  $V_{CC}$ . See the paragraph "ADC Noise Canceler" on page 211 on how to connect this pin.

Internal reference voltages of nominally 2.56V or AVCC are provided On-chip. The voltage reference may be externally decoupled at the AREF pin by a capacitor for better noise performance.

Figure 98. Analog to Digital Converter Block Schematic

#### Operation

The ADC converts an analog input voltage to a 10-bit digital value through successive approximation. The minimum value represents GND and the maximum value represents the voltage on the AREF pin minus 1 LSB. Optionally, AVCC or an internal 2.56V reference voltage may be connected to the AREF pin by writing to the REFSn bits in the ADMUX Register. The internal voltage reference may thus be decoupled by an external capacitor at the AREF pin to improve noise immunity.

The analog input channel and differential gain are selected by writing to the MUX bits in ADMUX. Any of the ADC input pins, as well as GND and a fixed bandgap voltage reference, can be selected as single ended inputs to the ADC. A selection of ADC input pins can be selected as positive and negative inputs to the differential gain amplifier.

If differential channels are selected, the differential gain stage amplifies the voltage difference between the selected input channel pair by the selected gain factor. This amplified value then

becomes the analog input to the ADC. If single ended channels are used, the gain amplifier is bypassed altogether.

The ADC is enabled by setting the ADC Enable bit, ADEN in ADCSRA. Voltage reference and input channel selections will not go into effect until ADEN is set. The ADC does not consume power when ADEN is cleared, so it is recommended to switch off the ADC before entering power saving sleep modes.

The ADC generates a 10-bit result which is presented in the ADC Data Registers, ADCH and ADCL. By default, the result is presented right adjusted, but can optionally be presented left adjusted by setting the ADLAR bit in ADMUX.

If the result is left adjusted and no more than 8-bit precision is required, it is sufficient to read ADCH. Otherwise, ADCL must be read first, then ADCH, to ensure that the content of the Data Registers belongs to the same conversion. Once ADCL is read, ADC access to Data Registers is blocked. This means that if ADCL has been read, and a conversion completes before ADCH is read, neither register is updated and the result from the conversion is lost. When ADCH is read, ADC access to the ADCH and ADCL Registers is re-enabled.

The ADC has its own interrupt which can be triggered when a conversion completes. When ADC access to the Data Registers is prohibited between reading of ADCH and ADCL, the interrupt will trigger even if the result is lost.

#### Starting a Conversion

A single conversion is started by writing a logical one to the ADC Start Conversion bit, ADSC. This bit stays high as long as the conversion is in progress and will be cleared by hardware when the conversion is completed. If a different data channel is selected while a conversion is in progress, the ADC will finish the current conversion before performing the channel change.

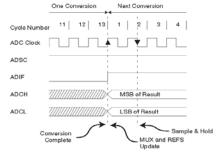

Alternatively, a conversion can be triggered automatically by various sources. Auto Triggering is enabled by setting the ADC Auto Trigger Enable bit, ADATE in ADCSRA. The trigger source is selected by setting the ADC Trigger Select bits, ADTS in SFIOR (see description of the ADTS bits for a list of the trigger sources). When a positive edge occurs on the selected trigger signal, the ADC prescaler is reset and a conversion is started. This provides a method of starting conversions at fixed intervals. If the trigger signal still is set when the conversion completes, a new conversion will not be started. If another positive edge occurs on the trigger signal during conversion, the edge will be ignored. Note that an Interrupt Flag will be set even if the specific interrupt is disabled or the global interrupt enable bit in SREG is cleared. A conversion can thus be triggered without causing an interrupt. However, the Interrupt Flag must be cleared in order to trigger a new conversion at the next interrupt event.

ADIF SOURCE 1

ADATE START

CLK<sub>ADD</sub>

CONVERSION

LOGIC

ADSC

Figure 99. ADC Auto Trigger Logic

Using the ADC Interrupt Flag as a trigger source makes the ADC start a new conversion as soon as the ongoing conversion has finished. The ADC then operates in Free Running mode, constantly sampling and updating the ADC Data Register. The first conversion must be started by writing a logical one to the ADSC bit in ADCSRA. In this mode the ADC will perform successive conversions independently of whether the ADC Interrupt Flag, ADIF is cleared or not.

If Auto Triggering is enabled, single conversions can be started by writing ADSC in ADCSRA to one. ADSC can also be used to determine if a conversion is in progress. The ADSC bit will be read as one during a conversion, independently of how the conversion was started.

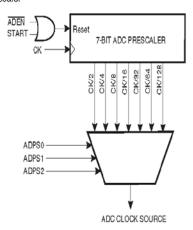

#### Prescaling and Conversion Timing

Figure 100. ADC Prescaler

By default, the successive approximation circuitry requires an input clock frequency between 50 kHz and 200 kHz to get maximum resolution. If a lower resolution than 10 bits is needed, the input clock frequency to the ADC can be higher than 200 kHz to get a higher sample rate.

The ADC module contains a prescaler, which generates an acceptable ADC clock frequency from any CPU frequency above 100 kHz. The prescaling is set by the ADPS bits in ADCSRA. The prescaler starts counting from the moment the ADC is switched on by setting the ADEN bit in ADCSRA. The prescaler keeps running for as long as the ADEN bit is set, and is continuously reset when ADEN is low.

When initiating a single ended conversion by setting the ADSC bit in ADCSRA, the conversion starts at the following rising edge of the ADC clock cycle. See "Differential Gain Channels" on page 209 for details on differential conversion timing.

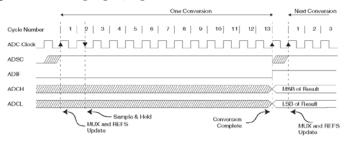

A normal conversion takes 13 ADC clock cycles. The first conversion after the ADC is switched on (ADEN in ADCSRA is set) takes 25 ADC clock cycles in order to initialize the analog circuitry.

The actual sample-and-hold takes place 1.5 ADC clock cycles after the start of a normal conversion and 13.5 ADC clock cycles after the start of a first conversion. When a conversion is complete, the result is written to the ADC Data Registers, and ADIF is set. In single conversion mode, ADSC is cleared simultaneously. The software may then set ADSC again, and a new conversion will be initiated on the first rising ADC clock edge.

When Auto Triggering is used, the prescaler is reset when the trigger event occurs. This assures a fixed delay from the trigger event to the start of conversion. In this mode, the sample-and-hold takes place 2 ADC clock cycles after the rising edge on the trigger source signal. Three additional CPU clock cycles are used for synchronization logic. When using Differential mode, along with Auto triggering from a source other than the ADC Conversion Complete, each conversion

will require 25 ADC clocks. This is because the ADC must be disabled and re-enabled after every conversion.

In Free Running mode, a new conversion will be started immediately after the conversion completes, while ADSC remains high. For a summary of conversion times, see Table 81.

Figure 101. ADC Timing Diagram, First Conversion (Single Conversion Mode)

Figure 102. ADC Timing Diagram, Single Conversion

Figure 103. ADC Timing Diagram, Auto Triggered Conversion

Figure 104. ADC Timing Diagram, Free Running Conversion

Table 81. ADC Conversion Time

| Condition                        | Sample & Hold (Cycles<br>from Start of<br>Conversion) | Conversion Time (Cycles) |

|----------------------------------|-------------------------------------------------------|--------------------------|

| First conversion                 | 13.5                                                  | 25                       |

| Normal conversions, single ended | 1.5                                                   | 13                       |

| Auto Triggered conversions       | 2                                                     | 13.5                     |

| Normal conversions, differential | 1.5/2.5                                               | 13/14                    |

#### ADC Conversion Result

After the conversion is complete (ADIF is high), the conversion result can be found in the ADC Result Registers (ADCL, ADCH).

For single ended conversion, the result is

$$ADC = \frac{V_{IN} \cdot 1024}{V_{REF}}$$

#### **Electrical Characteristics**

Absolute Maximum Ratings\*

| Absolute Maximum Hatings                                                            |

|-------------------------------------------------------------------------------------|

| Operating Temperature55°C to +125°C                                                 |

| Storage Temperature65°C to +150°C                                                   |

| Voltage on any Pin except RESET with respect to Ground0.5V to V <sub>CC</sub> +0.5V |

| Voltage on RESET with respect to Ground0.5V to +13.0V                               |

| Maximum Operating Voltage 6.0V                                                      |

| DC Current per I/O Pin40.0 mA                                                       |

| DC Current V <sub>CC</sub> and GND Pins 200.0mA PDIP and                            |

| 400.0mA TQFP/MLF                                                                    |

\*NOTICE:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC Characteristics

$T_A = -40$ °C to 85°C,  $V_{CC} = 2.7V$  to 5.5V (Unless Otherwise Noted)

| Symbol           | Parameter                                             | Condition                                                                                        | Min                                | Тур | Max                                | Units       |

|------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------|-----|------------------------------------|-------------|

| V <sub>IL</sub>  | Input Low Voltage except<br>XTAL1 and RESET pins      | V <sub>CC</sub> =2.7 - 5.5                                                                       | -0.5                               |     | 0.2 V <sub>CC</sub> <sup>(1)</sup> | ٧           |

| VIH              | Input High Voltage except<br>XTAL1 and RESET pins     | V <sub>CC</sub> =2.7 - 5.5                                                                       | 0.6 V <sub>CC</sub> <sup>(2)</sup> |     | V <sub>CC</sub> +0.5               | ٧           |

| V <sub>IH1</sub> | Input High Voltage<br>XTAL1 pin                       | V <sub>CC</sub> =2.7 - 5.5                                                                       | 0.7 V <sub>CC</sub> <sup>(2)</sup> |     | V <sub>CC</sub> +0.5               | ٧           |

| V <sub>IL1</sub> | Input Low Voltage<br>XTAL1 pin                        | V <sub>CC</sub> =2.7 - 5.5                                                                       | -0.5                               |     | 0.1 V <sub>CC</sub> <sup>(1)</sup> | ٧           |

| V <sub>IH2</sub> | Input High Voltage<br>RESET pin                       | V <sub>CC</sub> =2.7 - 5.5                                                                       | 0.9 V <sub>CC</sub> <sup>(2)</sup> |     | V <sub>CC</sub> +0.5               | ٧           |

| V <sub>IL2</sub> | Input Low Voltage<br>RESET pin                        | V <sub>CC</sub> =2.7 - 5.5                                                                       | -0.5                               |     | 0.2 V <sub>CC</sub>                | ٧           |

| V <sub>OL</sub>  | Output Low Voltage <sup>(3)</sup><br>(Ports A,B,C,D)  | I <sub>OL</sub> = 20 mA, V <sub>CC</sub> = 5V<br>I <sub>OL</sub> = 10 mA, V <sub>CC</sub> = 3V   |                                    |     | 0.7<br>0.5                         | <b>&gt;</b> |

| $V_{OH}$         | Output High Voltage <sup>(4)</sup><br>(Ports A,B,C,D) | I <sub>OH</sub> = -20 mA, V <sub>CC</sub> = 5V<br>I <sub>OH</sub> = -10 mA, V <sub>CC</sub> = 3V | 4.2<br>2.2                         |     |                                    | v<br>v      |

| I <sub>IL</sub>  | Input Leakage<br>Current I/O Pin                      | Vcc = 5.5V, pin low<br>(absolute value)                                                          |                                    |     | 1                                  | μА          |

| I <sub>IH</sub>  | Input Leakage<br>Current I/O Pin                      | Vcc = 5.5V, pin high<br>(absolute value)                                                         |                                    |     | 1                                  | μΑ          |

| R <sub>RST</sub> | Reset Pull-up Resistor                                |                                                                                                  | 30                                 |     | 60                                 | kΩ          |

| R <sub>pu</sub>  | I/O Pin Pull-up Resistor                              |                                                                                                  | 20                                 |     | 50                                 | kΩ          |

$T_{A}$  = -40°C to 85°C,  $V_{\rm CC}$  = 2.7V to 5.5V (Unless Otherwise Noted) (Continued)

| Symbol            | Parameter                                  | Condition                                                    | Min | Тур        | Max | Units |

|-------------------|--------------------------------------------|--------------------------------------------------------------|-----|------------|-----|-------|

|                   | Power Supply Current                       | Active 1 MHz, V <sub>CC</sub> = 3V<br>(ATmega 16L)           |     | 1.1        |     | mA    |

|                   |                                            | Active 4 MHz, V <sub>CC</sub> = 3V<br>(ATmega 16L)           |     | 3.8        | 5   | mA    |

|                   |                                            | Active 8 MHz, V <sub>CC</sub> = 5V (ATmega 16)               |     | 12         | 15  | mA    |

| I <sub>CC</sub>   |                                            | Idle 1 MHz, V <sub>CC</sub> = 3V<br>(ATmega 16L)             |     | 0.35       |     | mA    |

|                   |                                            | Idle 4 MHz, V <sub>CC</sub> = 3V<br>(ATmega 16L)             |     | 1.2        | 2   | mA    |

|                   |                                            | Idle 8 MHz, V <sub>CC</sub> = 5V<br>(ATmega 16)              |     | 5.5        | 7   | mA    |

|                   | Power-down Mode <sup>(5)</sup>             | WDT enabled, V <sub>GC</sub> = 3V                            |     | <8         | 15  | μА    |

|                   |                                            | WDT disabled, $V_{\rm CC} = 3V$                              |     | < 1        | 4   | μА    |

| V <sub>ACIO</sub> | Analog Comparator<br>Input Offset Voltage  | V <sub>CC</sub> = 5V<br>V <sub>in</sub> = V <sub>CC</sub> /2 |     |            | 40  | m∨    |

| I <sub>ACLK</sub> | Analog Comparator<br>Input Leakage Current | V <sub>CC</sub> = 5V<br>V <sub>in</sub> = V <sub>CC</sub> /2 | -50 |            | 50  | nA    |

| t <sub>ACPD</sub> | Analog Comparator<br>Propagation Delay     | V <sub>CC</sub> = 2.7V<br>V <sub>CC</sub> = 4.0V             |     | 750<br>500 |     | ns    |

### LAMPIRAN B2 DATA SHEET LM386

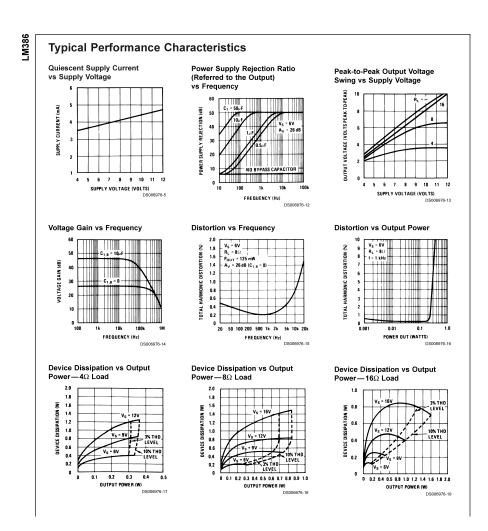

#### LM386

### Low Voltage Audio Power Amplifier

#### **General Description**

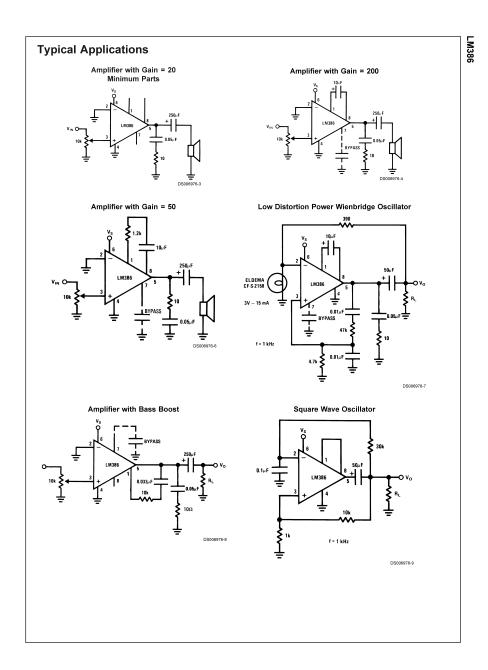

The LM386 is a power amplifier designed for use in low voltage consumer applications. The gain is internally set to 20 to keep external part count low, but the addition of an external resistor and capacitor between pins 1 and 8 will increase the gain to any value from 20 to 200.

The inputs are ground referenced while the output automatically biases to one-half the supply voltage. The quiescent power drain is only 24 milliwatts when operating from a 6 volt supply, making the LM386 ideal for battery operation.

#### **Features**

- Battery operation

- Minimum external parts

- Wide supply voltage range: 4V-12V or 5V-18V

- Low quiescent current drain: 4mA

- Voltage gains from 20 to 200

- Ground referenced input

- Self-centering output quiescent voltage

- Low distortion: 0.2% ( $A_V$  = 20,  $V_S$  = 6V,  $R_L$  = 8 $\Omega$ ,  $P_O$  = 125mW, f = 1kHz)

- Available in 8 pin MSOP package

#### **Applications**

- AM-FM radio amplifiers

- Portable tape player amplifiers

- Intercoms

- TV sound systems

- Line drivers

- Ultrasonic drivers

- Small servo drivers

- Power converters

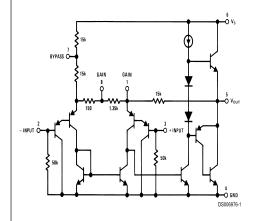

#### **Equivalent Schematic and Connection Diagrams**

Small Outline,

Top View

Order Number LM386M-1,

LM386MM-1, LM386N-1,

LM386N-3 or LM386N-4

See NS Package Number

M08A, MUA08A or N08E

| Absolute Maximum Ratings (Note 2)  If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications. |                 | Dual-In-Line Package<br>Soldering (10 sec)<br>Small Outline Package<br>(SOIC and MSOP)                                                 | +260°C  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|

| Supply Voltage                                                                                                                                                                                     |                 | Vapor Phase (60 sec)                                                                                                                   | +215°C  |  |  |

| (LM386N-1, -3, LM386M-1)                                                                                                                                                                           | 15V             | Infrared (15 sec)                                                                                                                      | +220°C  |  |  |

| Supply Voltage (LM386N-4)<br>Package Dissipation (Note 3)                                                                                                                                          | 22V             | V See AN-450 "Surface Mounting Methods and Their E<br>on Product Reliability" for other methods of soldering<br>surface mount devices. |         |  |  |

| (LM386N)                                                                                                                                                                                           | 1.25W           | Thermal Resistance                                                                                                                     |         |  |  |

| (LM386M)                                                                                                                                                                                           | 0.73W           | θ <sub>IC</sub> (DIP)                                                                                                                  | 37°C/W  |  |  |

| (LM386MM-1)                                                                                                                                                                                        | 0.595W          | θ <sub>IA</sub> (DIP)                                                                                                                  | 107°C/W |  |  |

| Input Voltage                                                                                                                                                                                      | ±0.4V           | θ <sub>IC</sub> (SO Package)                                                                                                           | 35°C/W  |  |  |

| Storage Temperature                                                                                                                                                                                | -65°C to +150°C | θ <sub>IA</sub> (SO Package)                                                                                                           | 172°C/W |  |  |

| Operating Temperature                                                                                                                                                                              | 0°C to +70°C    | θ <sub>IA</sub> (MSOP)                                                                                                                 | 210°C/W |  |  |

| Junction Temperature<br>Soldering Information                                                                                                                                                      | +150°C          | θ <sub>JC</sub> (MSOP)                                                                                                                 | 56°C/W  |  |  |

#### Electrical Characteristics (Notes 1, 2)

T<sub>A</sub> = 25°C

| Parameter                                  | Conditions                                                  | Min | Тур  | Max | Units |

|--------------------------------------------|-------------------------------------------------------------|-----|------|-----|-------|

| Operating Supply Voltage (V <sub>S</sub> ) |                                                             |     |      |     |       |

| LM386N-1, -3, LM386M-1, LM386MM-1          |                                                             | 4   |      | 12  | ٧     |

| LM386N-4                                   |                                                             | 5   |      | 18  | ٧     |

| Quiescent Current (I <sub>Q</sub> )        | V <sub>S</sub> = 6V, V <sub>IN</sub> = 0                    |     | 4    | 8   | mΑ    |

| Output Power (P <sub>OUT</sub> )           |                                                             |     |      |     |       |

| LM386N-1, LM386M-1, LM386MM-1              | $V_{\rm S}$ = 6V, $R_{\rm L}$ = 8 $\Omega$ , THD = 10%      | 250 | 325  |     | mW    |

| LM386N-3                                   | $V_S = 9V, R_L = 8\Omega, THD = 10\%$                       | 500 | 700  |     | mW    |

| LM386N-4                                   | $V_S = 16V, R_L = 32\Omega, THD = 10\%$                     | 700 | 1000 |     | mW    |

| Voltage Gain (A <sub>V</sub> )             | V <sub>S</sub> = 6V, f = 1 kHz                              |     | 26   |     | dB    |

|                                            | 10 μF from Pin 1 to 8                                       |     | 46   |     | dB    |

| Bandwidth (BW)                             | V <sub>S</sub> = 6V, Pins 1 and 8 Open                      |     | 300  |     | kHz   |

| Total Harmonic Distortion (THD)            | $V_S = 6V, R_L = 8\Omega, P_{OUT} = 125 \text{ mW}$         |     | 0.2  |     | %     |

|                                            | f = 1 kHz, Pins 1 and 8 Open                                |     |      |     |       |

| Power Supply Rejection Ratio (PSRR)        | V <sub>S</sub> = 6V, f = 1 kHz, C <sub>BYPASS</sub> = 10 μF |     | 50   |     | dB    |

|                                            | Pins 1 and 8 Open, Referred to Output                       |     |      |     |       |

| Input Resistance (R <sub>IN</sub> )        |                                                             |     | 50   |     | kΩ    |

| Input Bias Current (I <sub>BIAS</sub> )    | V <sub>S</sub> = 6V, Pins 2 and 3 Open                      |     | 250  |     | nΑ    |

$\textbf{Note 1:} \ \ \textbf{All voltages are measured with respect to the ground pin, unless otherwise specified.}$

Note 2: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

Note 3: For operation in ambient temperatures above 25°C, the device must be derated based on a 150°C maximum junction temperature and 1) a thermal resistance of 107°C/W junction to ambient for the dual-in-line package and 2) a thermal resistance of 170°C/W for the small outline package.

#### **Application Hints**

#### GAIN CONTROL

To make the LM386 a more versatile amplifier, two pins (1 and 8) are provided for gain control. With pins 1 and 8 open the 1.35  $\rm k\Omega$  resistor sets the gain at 20 (26 dB). If a capacitor is put from pin 1 to 8, bypassing the 1.35 k $\rm k\Omega$  resistor; the gain will go up to 200 (46 dB). If a resistor is placed in series with the capacitor, the gain can be set to any value from 20 to 200. Gain control can also be done by capacitively coupling a resistor (or FET) from pin 1 to ground.

Additional external components can be placed in parallel with the internal feedback resistors to tailor the gain and frequency response for individual applications. For example, we can compensate poor speaker bass response by frequency shaping the feedback path. This is done with a series RC from pin 1 to 5 (paralleling the internal 15 k $\Omega$  resistor). For 6 dB effective bass boost:  $R = 15 k\Omega$ , the lowest value for good stable operation is  $R = 10 k\Omega$  if pin 8 is open. If pins 1 and 8 are bypassed then R as low as  $2 k\Omega$  can be used. This restriction is because the amplifier is only compensated for closed-loop gains greater than 9.

#### INPUT BIASING

The schematic shows that both inputs are biased to ground with a 50 k $\Omega$  resistor. The base current of the input transistors is about 250 nA, so the inputs are at about 12.5 mV when left open. If the dc source resistance driving the LM386 is higher than 250 k $\Omega$  it will contribute very little additional offset (about 2.5 mV at the input, 50 mV at the output). If the dc source resistance is less than 10 k $\Omega$ , then shorting the unused input to ground will keep the offset low (about 2.5 mV at the input, 50 mV at the output). For dc source resistances between these values we can eliminate excess offset by putting a resistor from the unused input to ground, equal in value to the dc source resistance. Of course all offset problems are eliminated if the input is capacitively coupled.

When using the LM386 with higher gains (bypassing the 1.35 kΩ resistor between pins 1 and 8) it is necessary to bypass the unused input, preventing degradation of gain and possible instabilities. This is done with a 0.1  $\mu F$  capacitor or a short to ground depending on the dc source resistance on the driven input.

# LAMPIRAN C PROGRAM

/\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* This program was produced by the CodeWizardAVR V1.25.3 Standard Automatic Program Generator © Copyright 1998-2007 Pavel Haiduc, HP InfoTech s.r.l. http://www.hpinfotech.com Project: Version: Date : 6/13/2010 Author: F4CG Company: F4CG Comments: Chip type : ATmega16 : Application Program type Clock frequency : 12.000000 MHz Memory model : Small External SRAM size : 0 Data Stack size : 256 #include <mega16.h> #include <stdio.h> #include <delay.h> // Alphanumeric LCD Module functions #asm .equ \_\_lcd\_port=0x15 ;PORTC

#endasm

```

#include <lcd.h>

#define ADC_VREF_TYPE 0x40

// Read the AD conversion result

unsigned int read_adc(unsigned char adc_input)

{

ADMUX=adc_input | (ADC_VREF_TYPE & 0xff);

// Start the AD conversion

ADCSRA = 0x40;

// Wait for the AD conversion to complete

while ((ADCSRA \& 0x10) == 0);

ADCSRA = 0x10;

return ADCW;

}

// Declare your global variables here

int c,d,e,f,g,a,b,amp,fre,light,counter,cc,dd,ee,ff,gg,aa,bb,push,temp;

float sensitivity;

char

lcdamp[30],lcdfre[30],counter2[30],lcdc[30],lcdd[30],lcde[30],lcdf[30],lcdg[30],l

cda[30],lcdb[30],lcdpush[30],lcdsound[30];

//----piano sound-----

void doo(void)

{

counter=counter+1;

push=push+1;

```

```

OCR1A=22899.76336;

fre=262;

}

void re(void)

counter=counter+1;

push=push+1;

OCR1A=20407.16327;

fre=294;

}

void mi(void)

counter=counter+1;

push=push+1;

OCR1A=18180.81818;

fre=330;

}

void fa(void)

counter=counter+1;

push=push+1;

OCR1A=17190.97708;

fre=349;

}

void so(void)

{

```

```

counter=counter+1;

push=push+1;

OCR1A=15305.12245;

fre=392;

}

void la(void)

counter=counter+1;

push=push+1;

OCR1A=13635.36364;

fre=440;

}

void ti(void)

counter=counter+1;

push=push+1;

OCR1A=12144.74899;

fre=494;

}

//-----main-----

void main(void)

// Declare your local variables here

// Input/Output Ports initialization

// Port A initialization

```

```

// Func7=In Func6=In Func5=In Func4=In Func3=In Func2=In Func1=In

Func0=In

// State7=T State6=T State5=T State4=T State3=T State2=T State1=T State0=T

PORTA=0x00;

DDRA=0x00;

// Port B initialization

// Func7=In Func6=In Func5=In Func4=In Func3=In Func2=In Func1=In

Func0=In

// State7=T State6=T State5=T State4=T State3=T State2=T State1=T State0=T

PORTB=0x00;

DDRB=0x00;

// Port C initialization

// Func7=In Func6=In Func5=In Func4=In Func3=In Func2=In Func1=In

Func0=In

// State7=T State6=T State5=T State4=T State3=T State2=T State1=T State0=T

PORTC=0x00;

DDRC=0x00;

// Port D initialization

// Func7=Out Func6=In Func5=Out Func4=In Func3=In Func2=In Func1=In

Func0=In

// State7=0 State6=T State5=0 State4=T State3=T State2=T State1=T State0=T

PORTD=0x00;

DDRD=0xA0;

// Timer/Counter 0 initialization

// Clock source: System Clock

// Clock value: Timer 0 Stopped

// Mode: Normal top=FFh

```

```

// OC0 output: Disconnected

TCCR0=0x00;

TCNT0=0x00;

OCR0=0x00;

// Timer/Counter 1 initialization

// Clock source: System Clock

// Clock value: 12000.000 kHz

// Mode: CTC top=OCR1A

// OC1A output: Toggle

// OC1B output: Discon.

// Noise Canceler: Off

// Input Capture on Falling Edge

// Timer 1 Overflow Interrupt: Off

// Input Capture Interrupt: Off

// Compare A Match Interrupt: Off

// Compare B Match Interrupt: Off

TCCR1A=0x40;

TCCR1B=0x09;

TCNT1H=0x00;

TCNT1L=0x00;

ICR1H=0x00;

ICR1L=0x00;

OCR1AH=0x00;

OCR1AL=0x00;

OCR1BH=0x00;

OCR1BL=0x00;

// Timer/Counter 2 initialization

// Clock source: System Clock

// Clock value: 12000.000 kHz

```

```

// Mode: Fast PWM top=FFh

// OC2 output: Non-Inverted PWM

ASSR=0x00;

TCCR2=0x69;

TCNT2=0x00;

OCR2 = 0x00;

// External Interrupt(s) initialization

// INT0: Off

// INT1: Off

// INT2: Off

MCUCR=0x00;

MCUCSR=0x00;

// Timer(s)/Counter(s) Interrupt(s) initialization

TIMSK=0x00;

// Analog Comparator initialization

// Analog Comparator: Off

// Analog Comparator Input Capture by Timer/Counter 1: Off

ACSR=0x80;

SFIOR=0x00;

// ADC initialization

// ADC Clock frequency: 750.000 kHz

// ADC Voltage Reference: AVCC pin

// ADC Auto Trigger Source: None

ADMUX=ADC_VREF_TYPE & 0xff;

ADCSRA=0x84;

// LCD module initialization

```

```

lcd_init(16);

amp=0;

fre=0;

temp=0;

light=0;

push=0;

sensitivity=0.4;

while (1)

{

// Place your code here

//----analog to digital converter-----

amp=read_adc(0);

amp=amp/2;

c=read_adc(7);

d=read_adc(6);

e=read_adc(5);

f=read_adc(4);

g=read_adc(3);

a=read_adc(2);

b=read_adc(1);

sprintf(lcdc,"%4d",c);

sprintf(lcdd,"%4d",d);

sprintf(lcde,"%4d",e);

sprintf(lcdf,"%4d",f);

sprintf(lcdg,"%4d",g);

sprintf(lcda,"%4d",a);

sprintf(lcdb,"%4d",b);

```

```

sprintf(lcdamp,"%4d",temp);

sprintf(lcdfre,"%4d",fre);

sprintf(counter2,"%4d",counter);

sprintf(lcdpush,"%4d",push);

//-----calibration sensor-----

if (light==0)

cc=c*sensitivity;

dd=d*sensitivity;

ee=e*sensitivity;

ff=f*sensitivity;

gg=g*sensitivity;

aa=a*sensitivity;

bb=b*sensitivity;

light=1;

};

//-----PROGRAM PIANO-----

-----

//----none tuts state-----

if(c>=cc && d>=dd && e>=ee && f>=ff && g>=gg && a>=aa && b>=bb)

push=0;

temp=temp-2;

counter=0;

if (temp<1)

{

temp=0;

fre=0;

```

```

OCR1A=0;

};

OCR2=temp;

};

//----tuts sensor-----

if(c<cc)

{

doo();

};

if(d < dd)

{

re();

};

if(e<ee)

mi();

};

if(f < ff)

{

fa();

};

if(g < gg)

{

so();

};

if(a<aa)

{

la();

};

if(b<bb)

```

```

{

ti();

};

//----attack-----

if (amp>temp && push<15)

{

if (amp>225)

temp=200;

sprintf(lcdsound,"maxxx");

};

if(amp>150&&amp<=225)

{

temp=150;

sprintf(lcdsound,"keras");

};

if(amp>75&&amp<=150)

{

temp=100;

sprintf(lcdsound,"sdang");

};

if(amp <= 75)

{

temp=50;

sprintf(lcdsound,"lemah");

};

};

//-----decay-----

```

```

if (temp>0 && counter<=50)

{

temp=temp;

};

if (temp>0 && counter>50)

{

temp=temp-1;

};

if (temp<1)

fre=0;

temp=0;

};

//-----lcd------

lcd\_gotoxy(0,0);

lcd_putsf("am:");

lcd_gotoxy(4,0);

lcd_puts(lcdamp);

lcd_gotoxy(0,1);

lcd_putsf("fr:");

lcd_gotoxy(4,1);

lcd_puts(lcdfre);

lcd_gotoxy(11,0);

lcd_puts(lcdsound); // */

if(push>15)

{

OCR2=temp;

};

};

```

}

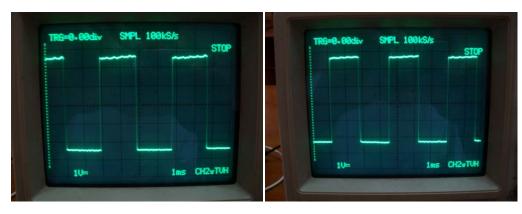

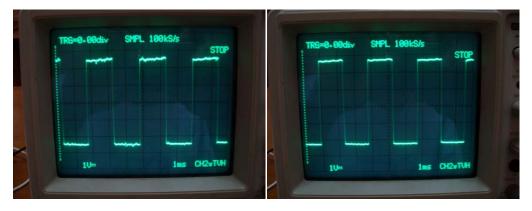

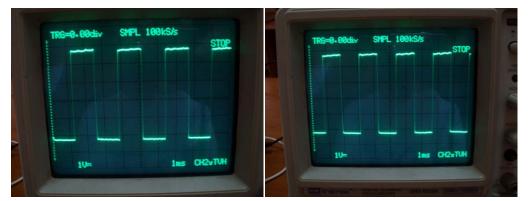

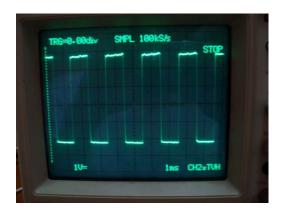

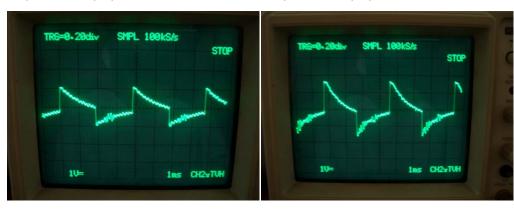

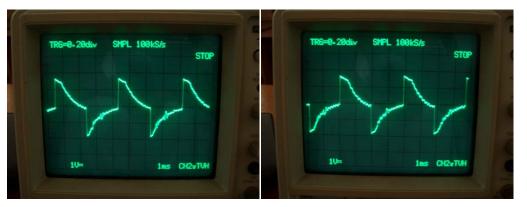

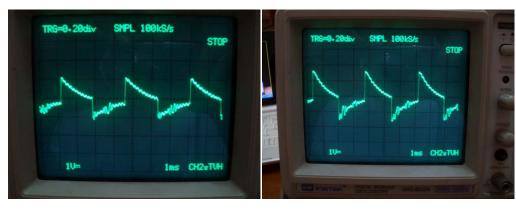

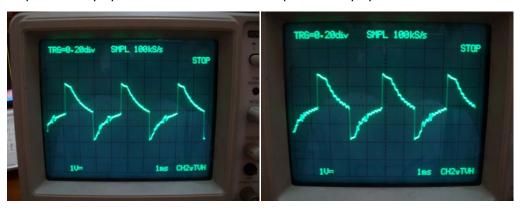

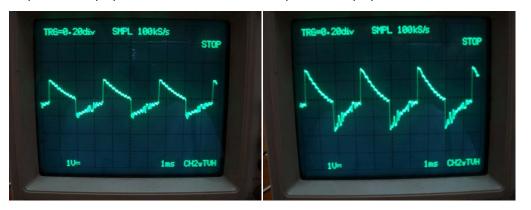

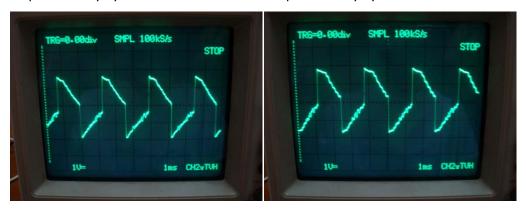

### LAMPIRAN D FOTO OSCILOSCOPE

#### Data Pada PWM

#### Nada Do

Nada Re

Nada Mi

Nada Fa

Nada So

Nada La

Nada Ti

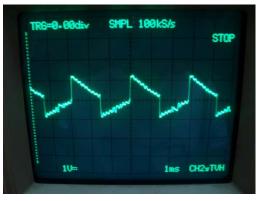

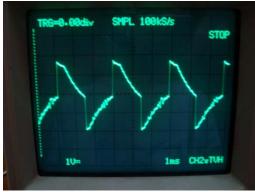

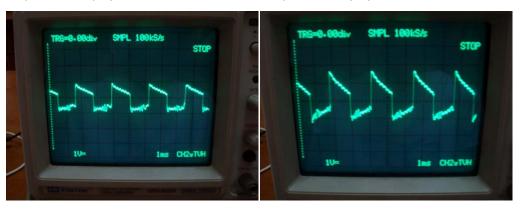

#### Data Pada Speaker

Nada Do Amplituda Duty Cycle 19.5%

Amplituda Duty Cycle 39.1%

Amplituda Duty Cycle 58.6%

Amplituda Duty Cycle 78.1%

Nada Re

Amplituda Duty Cycle 19.5%

Amplituda Duty Cycle 39.1%

Amplituda Duty Cycle 58.6%

Amplituda Duty Cycle 78.1%

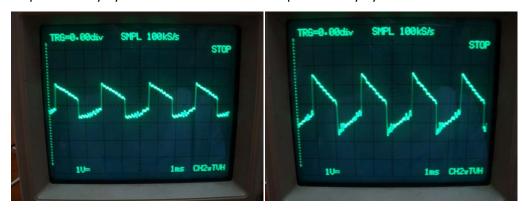

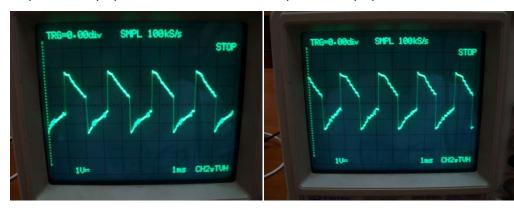

Nada Mi

Amplituda Duty Cycle 19.5%

Amplituda Duty Cycle 39.1%

Amplituda Duty Cycle 58.6%

Amplituda Duty Cycle 78.1%

TRS=0-20div SNPL 100kS/s STOP

Nada Fa Amplituda Duty Cycle 19.5%

Amplituda Duty Cycle 39.1%

Amplituda Duty Cycle 58.6%

Amplituda Duty Cycle 78.1%

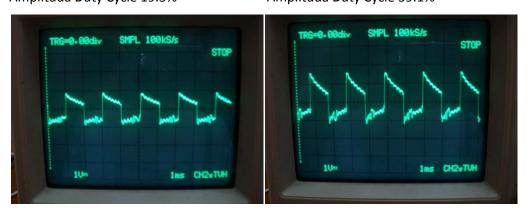

Nada So Amplituda Duty Cycle 19.5%

Amplituda Duty Cycle 39.1%

Amplituda Duty Cycle 58.6%

Amplituda Duty Cycle 78.1%

Nada Fa Amplituda Duty Cycle 19.5%

Amplituda Duty Cycle 39.1%

#### Amplituda Duty Cycle 58.6%

Amplituda Duty Cycle 78.1%

Nada Ti Amplituda Duty Cycle 19.5%

Amplituda Duty Cycle 39.1%

Amplituda Duty Cycle 58.6%

Amplituda Duty Cycle 78.1%